实际的应用中,DFN3*3、DFN5*6、SO8等封装类型的贴片元件,都会在PCB板器件位置的底部铺上一大片铜皮,然后器件底部框架的铜皮焊接在PCB的这一大片的

2023-02-16 11:13

一些电子公司的电路板来料中,经常发现焊前PCB没有任何起泡现象,但是焊好后却发现有些PCB板的板面绿油起泡,这是什么原因导致的,是板子有问题还是焊接工艺的问题?

2019-04-22 15:00

本文为您讲述PCB铜皮作为导线通过大电流,铜箔厚度(三种规格35um、50um、70um)不同宽度下载流量的参考数值,具体对照表及PCB电路板铜皮宽度和所流过电流量大小

2016-09-21 17:04

在PCB制造过程中,常见的PCB缺陷有:白斑、微裂纹、起泡、分层、湿织布、露织物、晕圈和阻焊缺陷。

2020-08-06 10:50

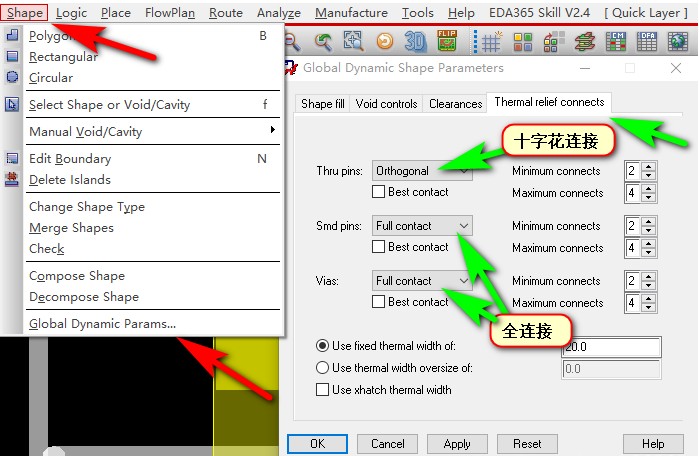

在PCB常规设计下,整板铜皮与焊盘的连接方式已经在Sbapa菜单栏下的Global Dynamic Shape Parameters选项下的Thermal relief connect选项栏中已经设置好了

2019-10-27 12:31

线路板厂的PCB组件在焊接后(包括再流焊、波峰焊),会在个别焊点周围出现浅绿色的小泡,严重时还会出现指甲盖大小的泡状物,不仅影响外观质量,严重时还会影响性能,一起了解一下PCB阻焊膜起泡的原因及解决方法。

2019-06-10 15:39

分层起泡区主要集中在控深钻孔区域,且该区域的孔壁铜层厚度不均匀;通过垂直切片,发现L7层附近的孔壁铜厚较薄的位置有微裂纹存在,且裂纹逐渐扩展延伸至L7/L8层芯板的玻纤和树脂界面之间,在外观上形成发白分层现象,说明分层起爆点位于控深钻孔孔壁铜厚较薄的区域。

2019-02-28 10:20

在Cadence Allegro16.6版本中,可以很方便的对Shape铜皮进行外扩或者内缩,而不需要重新绘制。

2018-12-02 11:16

Allegro中如何合并铜皮,这又是一篇有关Allegro操作的简短文章,同样是近期很多读者搜索的。Allegro中简单快捷的绘制Shape的操作,是我非常喜欢Allegro的一个原因,使用者可以轻易地绘制出各种需要的Shape。

2019-06-08 14:32

最近很多学员都很困惑如何设置铜皮到板框的距离,下面就来分享下一些小技巧,希望能给大家一些帮助。

2018-12-12 09:06