数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚

2020-11-22 11:54

今天给大家分享的是:PCB走线中需要注意的7个点。 一、PCB 电源布线 数字电路很多时候

2023-06-19 15:46

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走

2018-03-08 17:18

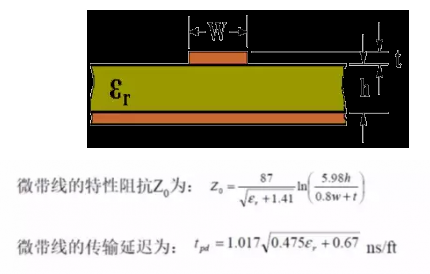

多长的走线才是传输线? 这和信号的传播速度有关,在FR4板材上铜线条中信号速度为6in/ns。简单的说,只要信号在走线上的往返时间大于信号的上升时间,

2020-11-06 10:25

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果

2019-03-15 14:05

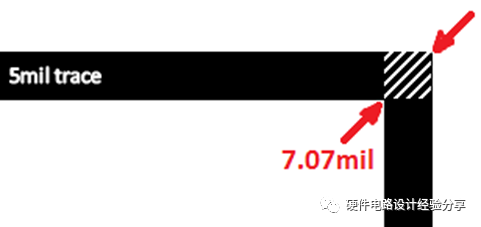

本期跟大家分享的是,为什么在PCB layout时不能走直角线?

2023-11-20 18:24

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线

2019-10-04 17:17

说到电磁干扰,大家都会不约而同的想说走线的问题,PCB材质引起的问题和周围环境的问题等等。关于材质问题,是我们不能决定的。我的建议就是在资金允许的范围内找大厂家并提出要求。对于周围环境的问题,可以

2020-09-14 09:51

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52