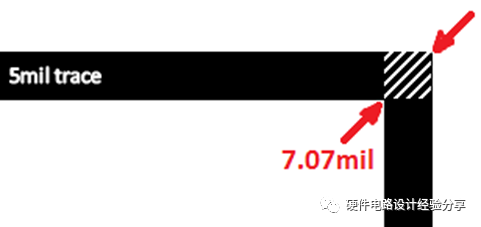

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以45度角走线,并且会说

2019-06-06 14:43

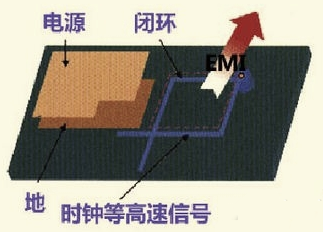

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

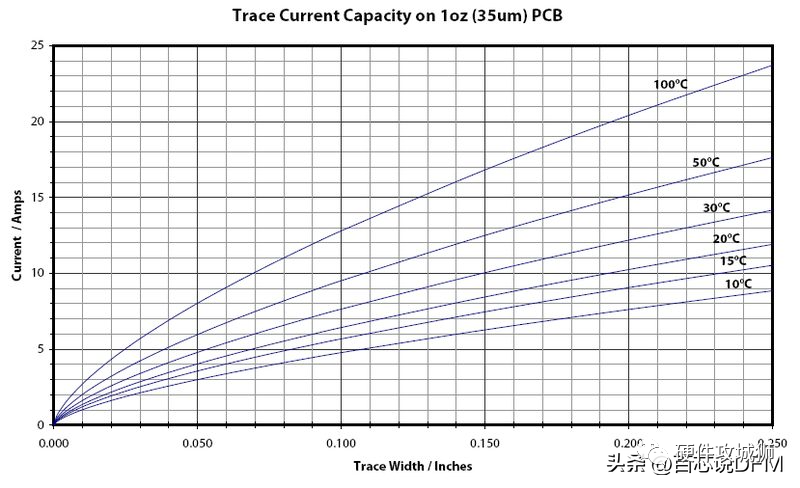

走线宽度是PCB设计中最关键的因素之一。

2023-07-12 13:53

IIC通信是一种双线制串行总线,由SDA(串行数据线)和SCL(串行时钟线)两条线组成。SDA线用于传输数据,而SCL线则用于传输时钟。在IIC通信中,数据的传输是由主设备发出开始信号,然后将数据发送给从设备,最后发出停止信号结束传输。

2023-08-26 12:02

当涉及到PCB 设计时,PCB 走线电流容量带来的限制是至关重要的。虽然IPC-2221通用设计指南是一个很好的起点,但 PCB

2022-08-22 09:05

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线一侧是VCC,另一侧是GND,那么哪个是参考平面?

2018-03-08 17:18

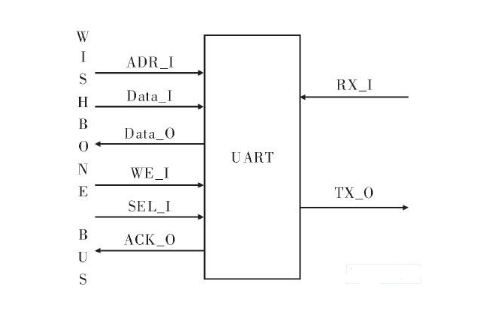

支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定义的标签是Wishbone规范区别与其他片上总

2018-07-06 08:07

电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4mil(或6mil),线间距不低于8mil;高密度板可采用4/6mil的线宽/间距,低密度版,尽量采用6/8mil的线宽/间距。信号线间距须遵循3W原则。

2019-10-25 14:16

本期跟大家分享的是,为什么在PCB layout时不能走直角线?

2023-11-20 18:24