在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

经常画高速板的同学都知道,10个高速板有9个要绕等长,而且内存出现的频率尤其频繁,整的现在画板子不绕两下都有点不习惯。好在上期给大家介绍了几种快的不能再快的绕等长的方法,用allegro绕等长还是非常任性的。看看下图

2018-11-11 10:55

高速PCB设计注意事项

2018-03-06 13:56

电路原理图的设计是整个电路设计的基础,它的设计的好坏直接决定后面PCB设计的效果。

2019-05-16 15:05

本文首先对高频电路板做了简单介绍,其次阐述了PCB设计高频电路板布线技巧,最后介绍了PCB设计高频电路板布线注意事项

2018-10-14 11:49

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。

2019-03-19 17:30

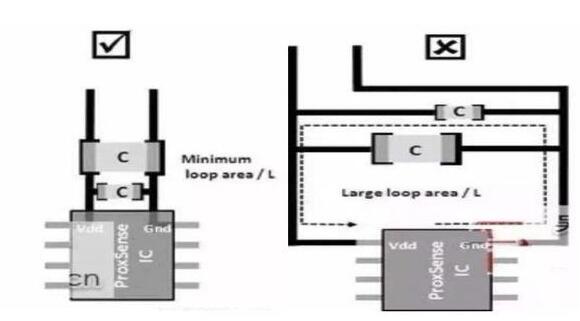

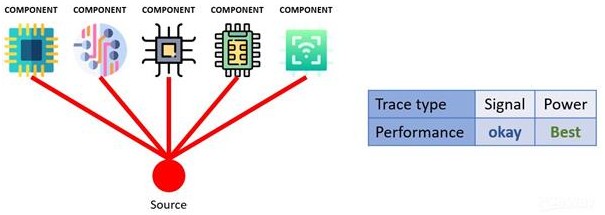

随着对高速电路需求的不断增加,PCB设计变得越来越具有挑战性。对于PCB上的设计,工程师必须考虑影响电路的几个方面,如功耗,PCB尺寸,环境噪声和EMC。以下将介绍硬件工程师如何解决EMC相关问题的方式方法。

2020-07-09 15:24

在PCB设计,到最后进行PCB量产的时候,PCB拼板也是一件非常重要的事,这不仅牵涉到PCB电路板的质量标准,更能影响PCB

2019-02-24 09:37

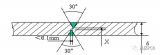

PCB设计是电子工程师最基本技能,同时也是最重要的技能之一。PCB线路的转角、长短、EMI、阻抗等因素时时刻刻影响着电路板的工作性能。本文为工程师总结了在PCB设计当中应该注意

2014-09-04 14:10

在设计PCB时,我们通常会依赖以前在网上通常会找到的经验和技巧。每个PCB设计都可以针对特定应用进行优化,通常,其设计规则仅适用于目标应用。例如,模数转换器PCB规则不适用于RF

2021-04-27 09:56