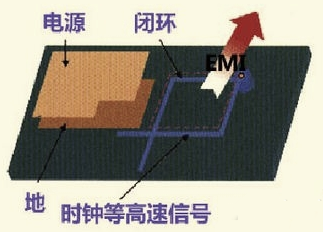

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-03-15 14:05

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35

本文主要介绍的是pcb开窗,首先介绍了PCB设计中的开窗和亮铜,其次介绍了如何实现PCB走线开窗上锡,最后阐述了PCB设计

2018-05-04 15:37

IIC通信是一种双线制串行总线,由SDA(串行数据线)和SCL(串行时钟线)两条线组成。SDA线用于传输数据,而SCL线则用于传输时钟。在IIC通信中,数据的传输是由主设备发出开始信号,然后将数据发送给从设备,最后发出停止信号结束传输。

2023-08-26 12:02

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线每1000mil打孔接地 。 高速信号的

2023-05-22 09:15

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

2019-02-05 08:49

电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4mil(或6mil),线间距不低于8mil;高密度板可采用4/6mil的线宽/间距,低密度版,尽量采用6/8mil的线宽/间距。信号线间距须遵循3W原则。

2019-10-25 14:16

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-07-01 15:24

线宽要按50或者100欧姆设计,差分线要做等长,电源走线要粗一点,电源地平面最好紧耦合等等这些PCB设计的常规操作相信没人质疑。那么对于

2021-03-29 11:46