本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解误区。 误区一:GHz速率以上的信号才算高速信号

2019-11-05 11:27

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

一前言在电子设备中,随着电路集成度不断提高以及工作频率持续上升,电磁兼容性(EMC)成为关键问题。信号走线作为电路中信号传输的通道,其长度对辐射发射有着显著影响,这不仅关系到设备自身的稳定运行,还关

2025-08-05 11:33 深圳市韬略科技有限公司 企业号

本文首先介绍了PCB信号完整性的问题,其次阐述了PCB信号完整性的步骤,最后介绍了如何确保PCB设计

2018-05-23 15:08

高频信号一般使用串行阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的

2023-09-12 17:32

所有电流必须有流回源的回路。该回路的产生会自动寻找最小阻抗的路径。通常在具有电源/地层平面的PCB结构中,会直接在信号线下方的平面上(电源或地)。该回流信号(电流)与原信号

2019-09-11 11:47

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组

2019-03-19 17:30

高扇出信号线 (HFN) 是具有大量负载的信号线。作为用户,您可能遇到过高扇出信号线相关问题,因为将所有负载都连接到 HFN 的驱动程序需要使用大量布线资源,并有可能导致布线拥塞。鉴于负载分散,导致进一步增大

2025-08-28 10:45

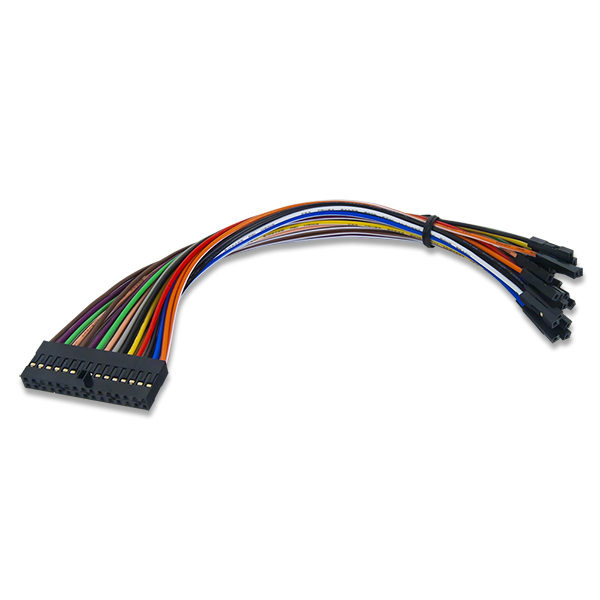

Analog Discovery信号线组件,或称Flywire,是与Analog Discovery产品原装信号线相同的组件。

2019-11-26 11:08

虽然通过增加走线宽度可以减少20%的自感,但减少50%走线的长度,减少50%的自感。相对而言,走线宽度必须增加5倍,以减少50%的自感。

2020-10-10 11:40