在高速PCB设计中,对于射频信号的走线,其相邻层挖空的设计具有重要作用。射频信号通常需要严格控制阻抗(如50Ω),当射频走线线宽增加以降低插入损耗时,参考层距离的增加是必要的。通过挖空相邻层,以至于

2025-06-11 17:08

在高速PCB设计中,对于射频信号的焊盘,其相邻层挖空的设计具有重要作用。首先射频信号的焊盘通常较大,容易形成分布电容,从而破坏微带线或带状线的特性阻抗连续性。通过在焊盘正下方的相邻层挖空处理,可以

2025-06-06 11:47

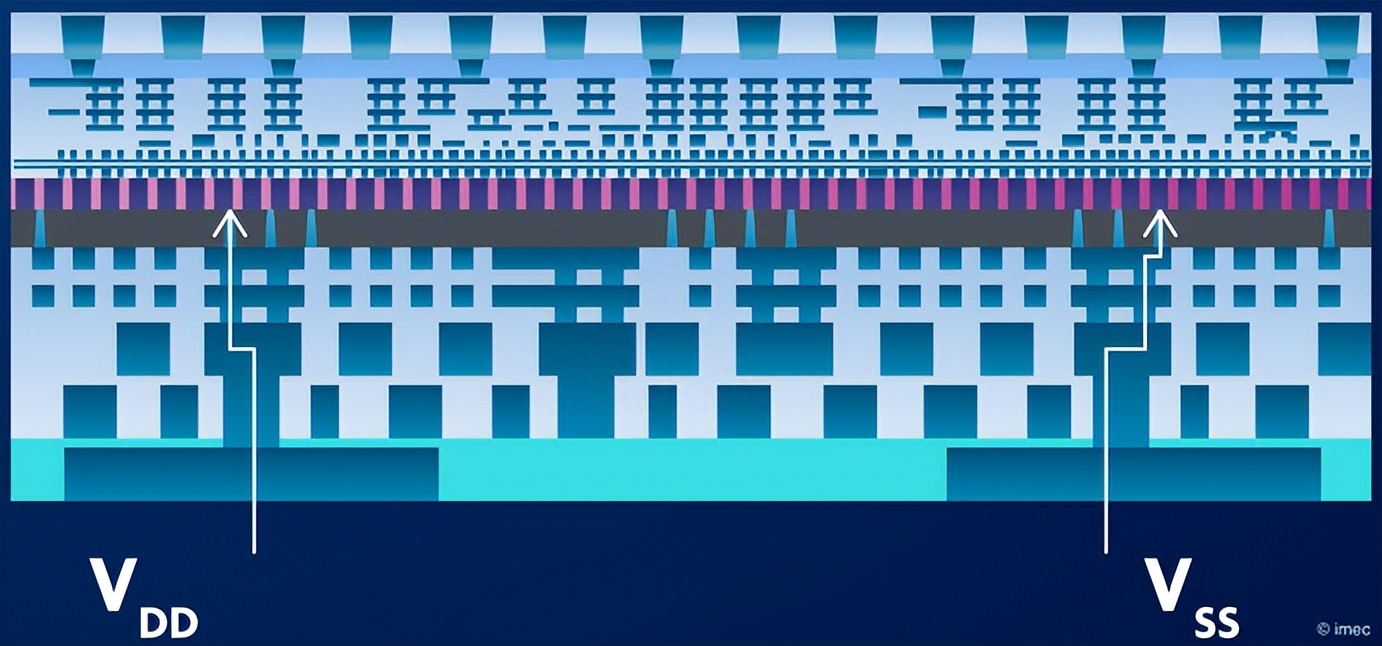

英特尔表示,它是业内第一个在类似产品的测试芯片上实现背面供电的公司,实现了推动世界进入下一个计算时代所需的性能。PowerVia 将于 2024 年上半年在英特尔 20A 工艺节点上推出,正是英特尔业界领先的背面供电

2023-06-20 15:39

在一些晶振的PCB设计中,相邻层挖空(净空)或者同一层和相邻层均净空处理,第三层需要有完整的地平面,这么做的原因是维持负载电容的恒定。

2020-11-17 14:54

一、概述 晶圆背面涂敷工艺是在晶圆背面涂覆一层特定的材料,以满足封装过程中的各种需求。这种工艺不仅可以提高芯片的机械强度,还可以优化散热性能,确保芯片的稳定性和可靠性。

2024-12-19 09:54 广州万智光学技术有限公司 企业号

英特尔率先在产品级芯片上实现背面供电技术,使单元利用率超过90%,同时也在其它维度展现了业界领先的性能。 英特尔宣布在业内率先在产品级测试芯片上实现背面供电(backs

2023-06-06 16:22

,整个配电网络被移至晶圆的背面。硅通孔(TSV)将电源直接从背面传送到正面,而无需电子穿过芯片正面上日益复杂的后道工序(BEOL)堆栈。 图1. 背面供电网络的示意图,

2023-09-05 16:39

近日,新思科技(Synopsys)宣布了一项重大的技术突破,成功推出了1.6纳米背面电源布线项目。这一技术将成为未来万亿晶体管芯片制造过程中的关键所在。

2024-09-30 16:11

英特尔宣布在业内率先在产品级测试芯片上实现背面供电(backside power delivery)技术,满足迈向下一个计算时代的性能需求。作为英特尔业界领先的背面供电 解决方案,PowerVia

2023-06-09 20:10

背面实施流程已通过成功的 SF2 测试芯片流片得到验证。这是 2nm 设计的一项关键功能,但可能会受到三星、英特尔和台积电缺乏布线的限制,而是在晶圆背面布线并使用过孔连接电源线。

2023-07-05 09:51