在PCB设计中,“间距”绝对是个绕不开的重要话题。

2025-04-15 16:18

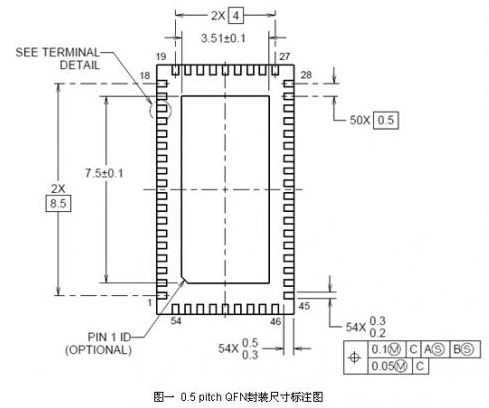

QFN封装的引脚间距较小是指在该封装中,相邻引脚之间的距离相对较小。这种设计有助于减小整体封装的尺寸,使芯片的集成更加紧凑,从而在有限的空间内容纳更多的

2024-02-23 09:48

比如覆铜间距16mil,其他安全间距8mil,过孔到过孔间距100mil,焊盘到过孔间距100mil,顶层地覆铜0.8mm,顶层VCC3.3与VCC1.8覆铜

2018-12-27 08:46

W1.0mm。整个字符的高度H1.2mm。字符之间的间距D0.2mm。当文字小于以上标准时加工印刷出来会模糊不清。

2019-05-31 16:35

芯片的引脚是指芯片上的金属引脚,它们起着连接芯片与外部电路的作用。每个引脚

2023-07-25 09:50

识别集成芯片的引脚和引脚功能是电子工程师和爱好者在设计和维修电子设备时的基本技能。以下是一些关键步骤和技巧,帮助您准确地识别和理解集成芯片的

2024-03-21 15:58

集成芯片的引脚顺序一般遵循特定的排列规则,以确保电路的正常工作。不同的芯片型号和封装方式可能有不同的引脚排列方式。

2024-03-19 17:18

一些引脚被焊接或压接到电线上,但是引脚(例如插头,焊料安装座,压入配合和转塔样本)被安装在PCB上。

2021-01-29 10:37

在PCB设计中,QFN封装的器件通常使用微带线从TOP或者BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。

2019-10-04 17:09

集成芯片内部的引脚排列原理是确保电路正常工作的重要基础。引脚,作为芯片与外部电路的连接点,其排列方式直接影响到电路的连接和信号传输。

2024-03-21 15:43