因为设计需要,要在PCB里绘制螺旋线的走线作为高频电路的天线,如果直接使用AD基本上很难完成这样的绘图操作。

2018-11-12 09:10

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度

2018-06-16 07:17

原理图是电路的逻辑和视觉表示。这是电子产品设计的第一步。早些时候,设计人员过去常常在纸上绘制电路图。现在,他们已经开始使用简化了设计流程的 PCB 设计工具(M-CAD 和 E-CAD)。建议设计人员遵循标准原理图指南,以获得结构良好且无错误的设计。

2022-10-08 09:26

注:如果在绘制原理图的过程中出现了错误,但是PCB的布局都已经弄好了,想要把错误改过来而不影响PCB布局,那么也是操作此步骤,只是在最后一项Add ROOMS的那一项前面的Add不要勾选!!!否则会重新布局,那是痛苦

2018-04-19 14:18

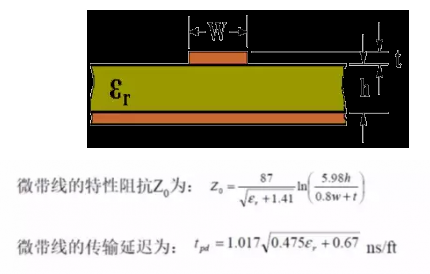

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17

本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

DDR5标准JESD79-5文件中没有明确的控制阻抗建议,DDR4时代基本内存条上时钟阻抗还是跟着芯片、主板走的70-80欧姆。线宽相对而言比较细。不知道你开始使用DDR5没有,你有关注过

2024-07-16 17:47

上一章讲述了如何利用现有的元件符号绘制原理图,但是有很多元件是库里没有的,这就需要我们自己来绘制元件符号,以之前学过的STC89C52RC单片机为例,这个元件在库里是没有的,现在我们来绘制这个元件,首先打开原理图库文

2023-03-02 09:46

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径),最常见的传输线也就是我们PCB板上的走

2020-11-06 10:25