在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。

2022-11-02 09:25

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition PCB

2018-05-15 10:49

经常画高速板的同学都知道,10个高速板有9个要绕等长,而且内存出现的频率尤其频繁,整的现在画板子不绕两下都有点不习惯。好在上期给大家介绍了几种快的不能再快的绕等长的方法,用allegro绕等长还是非常任性的。看看下图

2018-11-11 10:55

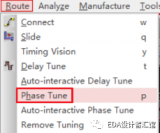

有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从有了绕线新功能,就再也不担心绕

2018-10-19 15:33

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。

2019-03-19 17:30

上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制。

2018-11-29 15:34

本文介绍了一种计算检流放大器直流误差的系统方法,对每个误差源展开讨论,介绍了一种估算总误差的方法。最后,文章还介绍了计算

2014-01-26 10:05

从早期的15.x版本到如今依然运用广泛的16.5版本,不管是差分对内还是组间,绕等长的命令只有一个Delay Tune可以用,不过就这一个命令从速度上来讲依然比其他软件要快。

2018-07-20 15:27

本例中需要实现PCI-e金手指到EMMC芯片等长,包括D0-D7,CLK,CMD这10条网络。查看各条网络,确认是否存在串联匹配电阻。本例中,仅在时钟线上存在,如下图的高亮器件。

2019-06-22 09:44