目前用户最需要是一个时序分析和SI结合一体工具,而且界面要优化,设置要简单,同时需要包括Design KIT。ICX Tau如果能够象Quantum-SI一样性能得到改进,那么将

2010-10-26 15:46

Cadence PCB SI分析特性阻抗变化因素教程 Cadence 的PCB SI工具是一个强大的SI分析软件,下面

2010-03-21 18:37

,高密度PCB板上的高速讯号或频率走线则会对间距越来越小的相邻走线产生很难准确量化的串扰与EMC问题。SI和EMC的问题将会导致PCB设计过程的反复,而使得产品的开发周期一再延误。

2018-05-22 07:18

时序问题最为重要,目前设计者基本上采用核心芯片厂家现成方案,因此设计中主要一部分工作是如何保证PCB能够符合芯片工作要求时序。

2019-12-26 17:28

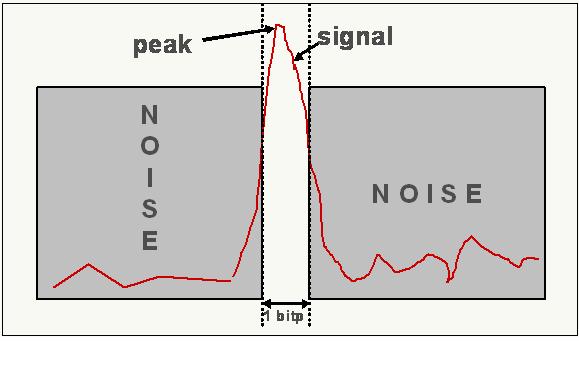

信号通过信道传输时会发生降级。高速信号特别容易降级,因为损耗和失真往往与频率有关。

2019-09-10 17:38

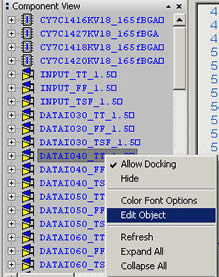

Allegro PCB SI环境中目前有多种模型编辑选项。这些包括PCB SI和SigXplorer环境中的传统对话框。虽然这些对话框提供图形编辑,但它们通过多个级别级

2019-09-01 09:53

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立元件的建模,而芯片IO和连接器的模型通常会由原厂提供。

2020-09-08 11:56

其二,从Cadence SPB 16.5版本开始,Allegro PCB SI名义上也直接支持IBIS模型,所以可以保留现有的两个IBIS文件不做转换,然后在之后的仿真中直接调用。之所以说是“名义上

2021-03-04 16:38

随着数据中心的快速发展,交换机单lane信号速率也在飞速提升,这对PCB和SI设计而言都是全新的挑战。本文将从PCB的硬件设计与加工两个维度来阐述,如何提升交换机56G信号传输的可靠性。

2022-09-22 10:23

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立元件的建模,而芯片IO和连接器的模型通常会由原厂提供。

2018-08-04 10:01