在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建

2019-03-15 14:05

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另

2019-10-13 13:19

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚

2020-11-22 11:54

多长的走线才是传输线? 这和信号的传播速度有关,在FR4板材上铜线条中信号速度为6in/ns。简单的说,只要信号在走线上的往返时间大于信号的上升时间,PCB上的走线就应

2020-11-06 10:25

对于PCB工程师来说,最关注的还是如何确保在实际走线中能完全发挥差分走线的这些优势。也许只要是接触过Layout的人都会了解差分走线的一般要求,那就是“等长、等距”。等

2019-12-30 15:12

今天我们讲一下与时钟(clock)相关的PCB的设计考虑,主要分两部分:原理图设计 - 针对时钟电路应该放置哪些器件?以及PCB布局和走

2018-11-25 11:09

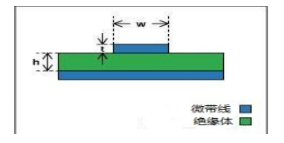

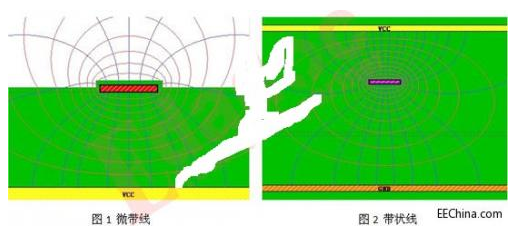

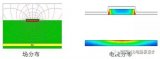

PCB中的信号线分为两种,一种是微带线,一种是带状线。 微带线,是走在表面层(microstrip),附在

2020-09-30 10:38

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一个通道传播,串行信号对和

2019-09-20 14:12

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线一侧是VCC,另一侧是GND,那么哪个是参考平面?

2018-03-08 17:18