由上电时序可知,VDD_SOC_IN上电时序要迟于VDD_HIGH_IN

2018-04-28 09:57

时序以及各阶段I/O 管脚状态,说明了FPGA上电配置对电路功能的严重影响,最后针对不同功能需求的FPGA外围电路提出了有效的设计建议。

2017-11-22 07:18

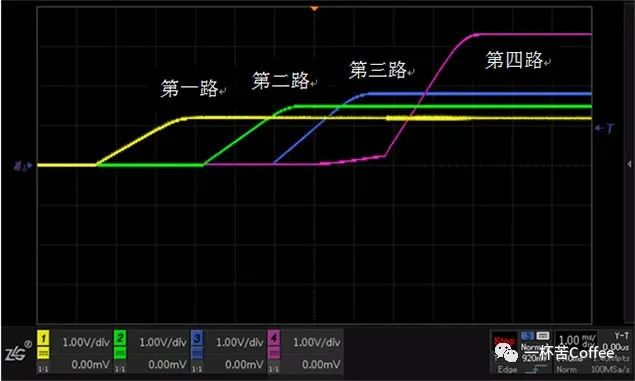

为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?

2017-04-19 10:42

电源时序控制是微控制器、FPGA、DSP、 ADC和其他需要多个电压轨供电的器件所必需的一项功能。##通过将衰减版本的调节器输出端连接至待上

2014-08-05 10:15

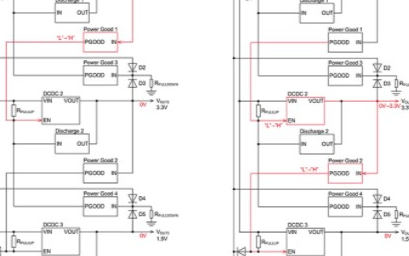

上一篇文章中介绍了使用通用电源IC实现电源时序控制电路的“电源时序规格①”的控制电路。本文先介绍使用通用电源IC实现电源

2022-01-18 14:50

上电时序(Power-up Sequeence)是指各电源轨上电的先后关系。 与之对应的是下

2023-12-11 18:17

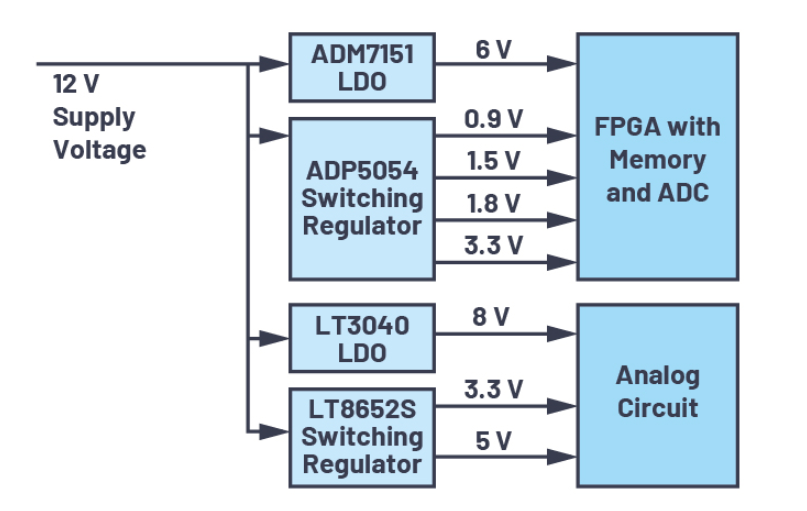

丰富的应用特性。这些设备向电源系统提供不同的数字负载,要求使用不同功率等级的多种电压轨,每一种都具有高度个性化的电压轨容差。同样,正确的电源开启和关断时序也很重要。随着时间推移,电路板上电压轨的数量成倍增加,使得电源系统的时

2022-01-21 10:51

比如说电源的上电时序,我们需要注意系统电源的上升时间,很多人不理解, 上电就上电

2018-11-11 11:08

当今的电子应用常常需要不止一个5 V或3.3 V电源电压。10个、20个或更多的电压并不罕见。此外,有的电压域具有相同的电压电平,但必须作为单独的域产生——也就是说,这些电压必须产生两次。一个例子是提供两个相同的电压来分别为模拟和数字负载供电。这种分离可防止相互干扰,并在不同时间为不同负载提供能量。

2022-08-03 18:12