Xilinx推荐对于低扇出的触发器控制信号在代码编写时尽量吸收进触发器D输入端之前的LUT中,并在XST的综合属性选项中提供配置项,让XST综合时自动将低扇出的控制信号

2023-12-14 15:04

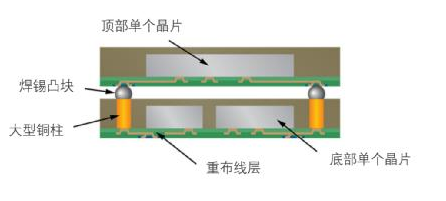

扇出型封装一般是指,晶圆级/面板级封装情境下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。扇出型封装的核心要素就是芯片上的RDL重布线层(可参考下面图表说明

2023-11-27 16:02

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17

Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化

2019-10-13 14:55

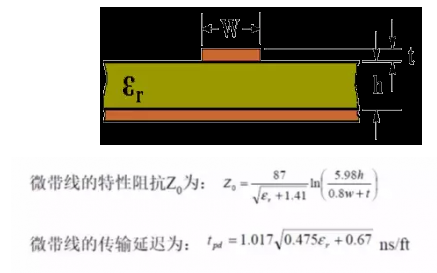

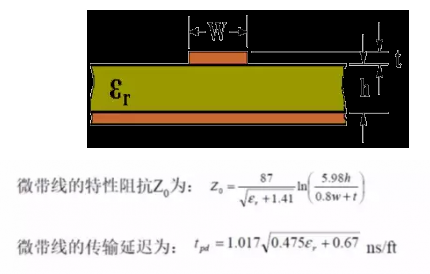

阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去

2019-09-06 11:52

高密度扇出型封装技术满足了移动手机封装的外形尺寸与性能要求,因此获得了技术界的广泛关注。

2020-07-13 15:03

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2018-10-14 09:28

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17

RDL 技术是先进封装异质集成的基础,广泛应用扇出封装、扇出基板上芯片、扇出层叠封装、硅光子学和 2.5D/3D 集成方法,实现了更小、更快和更高效的芯片设计。

2024-03-01 13:59

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,

2017-11-26 14:28