添加类:做等长处理的往往是多根线,需要将多根线归成一类,设置netclass方法如下:在原理图中:Place-directives-BlanketPlace-directives-NetClass标记结果如下:仅作参考,比如将电源归位电源类

2019-05-24 08:57

本帖最后由 一只耳朵怪 于 2018-6-25 14:19 编辑 1、在对6678中SRIO进行PCB布线时遇到一个疑问。若需要使用SRIO 4X模式时,PCB布线是否有必要对4组TX和RX差分信号分别进行等长处理

2018-06-25 04:40

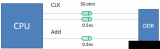

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29

因为第一次做等长线处理,业务不熟练,在网上也看了各类教程,单实际画的时候又是另外一回事,能请各位大神帮我指出图中的问题点吗?万分感谢,你那个有具体的指导建议就更完美了!

2019-08-07 16:07

的讲解数据线等长设计。 在另一个文件《AD设计DDR3时等长设计技巧-地址线T型等长》中着重讲解使用AD设计DDR地址线走线T型走线等长处理的方法和技巧。

2025-07-28 16:33

怎么做CANopen开发

2017-09-27 12:30

pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷电路板)设计和制造过程中,通过优化电气特

2024-01-17 16:38

我们俗称的 PCB 信号等长处理。等长的目标是为了满足同组信号的时序匹配要求。 2、等长范围应严格遵守不同接口或者信号的要求,具体的可参考模块规范内容。如若有疑问,及时

2023-07-27 07:40

/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时

2018-03-23 10:05

`如附图所示的多个DDR2地址线走线等长大家是怎么做的(用pads),大家有什么好的方法吗?共享一下,谢谢!`

2013-08-05 11:09