数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

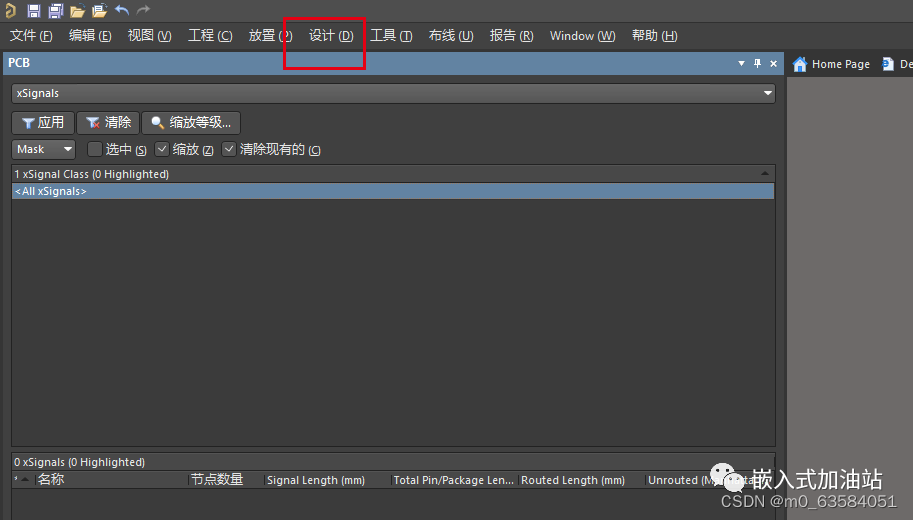

1.将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入

2018-05-22 10:45

PCB设计中常见的走线等长要求

2023-11-24 14:25

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29

Bus/总线布线时如何做到等长 Bus走线模式是在13.6版本中可以实现的模式,现在14.x以及15.0都已

2009-09-28 12:45

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走

2023-07-27 07:40

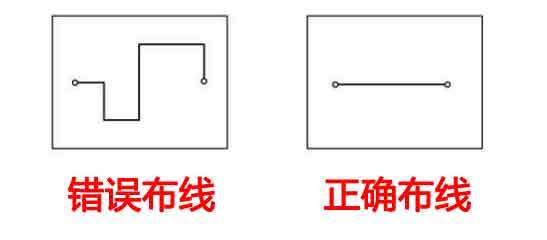

毫无疑问,布线是整个PCB设计中最重要、最费时的工序,直接影响着 PCB 板的性能好坏。作为一名合格的、优秀的PCB设计工程师,除了要把

2022-02-12 11:21

布线是 PCB 设计的重要组成部分,也是整个 PCB 设计中工作量最大和最耗时间的部分,工程师在进行 PCB 布线工作时

2023-02-02 14:46

等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27