我无法找到解释为什么人们想要沿着铜迹线(或PCB上的任何地方)放置尽可能多的通孔(~50),这些通孔传输高频RF(100 MHz至GHz)信号。 在我的情况下,我的电路板两侧有两个地平面(倾倒)。我

2021-02-23 11:44

必须确保测量精度不受PCB或测试装置的杂散电容和电感影响。您可以通过使用低电容探头、在PCB上使用短连接线,并且避免在信号走线下大面积铺地来尽可能规避这些问题。

2023-04-17 09:16

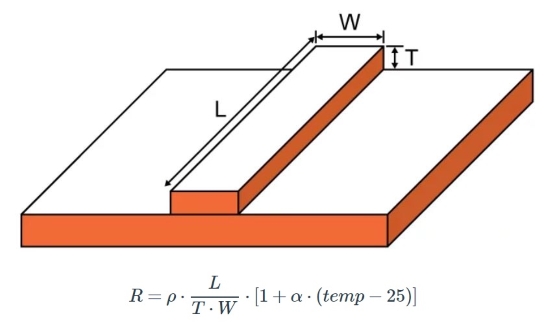

使栅极驱动布线尽可能宽并尽可能短。1oz覆铜对应20mil的布线宽度,如果是大电流,

2022-08-15 09:18

在测量运算放大器输入电容时,应关注哪些方面? 必须确保测量精度不受PCB或测试装置的杂散电容和电感影响。您可以通过使用低电容探头、在PCB上使用短连接线,并且避免在信号走线下大面积铺地来

2023-04-11 03:45

TI 工程师在本视频中介绍了如何在 QFN 封装芯片的 PCB 设计上得到尽可能好的串扰性能。 主要分三章进行讲解: 第一、 QFN 封装简介; 第二、如何最小化 PCB 设计上的串扰; 第三、仿真

2017-04-18 01:50

接地层可改善电路的电气特性,同时还可简化布局任务,并在某些情况下缩小PCB尺寸。

2019-09-06 05:21

印刷导线应尽可能短;统一组件的地址线或数据线应尽可能长;当电路为高频电路或布线密集时,印刷导线的角应为圆形。否则,它会影响电路的电气特性。

2020-05-28 08:42

在UPS 的实际应用中,温度对电池的自然老化过程有很大影响。详细的实验数据表明温度每上升 5℃,电池寿命就下降 10%,所以 UPS 蓄电池的设计应让电池保持尽可能的温度。

2020-08-09 15:22

本指南旨在说明如何尽可能地加强Linux的安全性和隐私性,并且不限于任何特定的指南。 免责声明:如果您不确定自己在做什么,请不要尝试在本文中使用任何内容。 本指南仅关注安全性和隐私性,而不关注性能

2021-04-25 14:58

通过EMC的要求。 以下仅就PCB板的设计技巧提供几个降低电路产生的电磁辐射效应。 1、尽可能选用信号斜率(slew rate)较慢的器件,以降低信号所产生的高频成分。 2、注意高频器件摆放的位置,不要太靠近对外的连接器。 3、注意高速信号的阻抗匹配,走线层及其回

2021-06-24 16:02