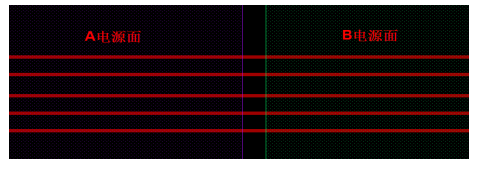

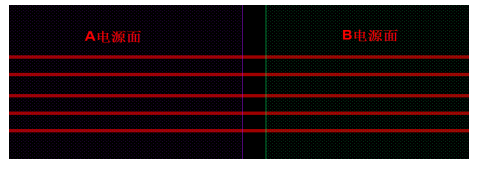

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整

2022-12-23 09:34

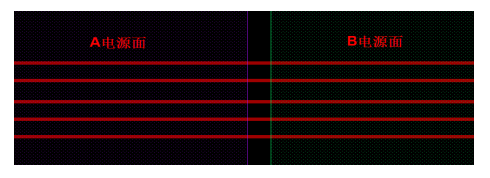

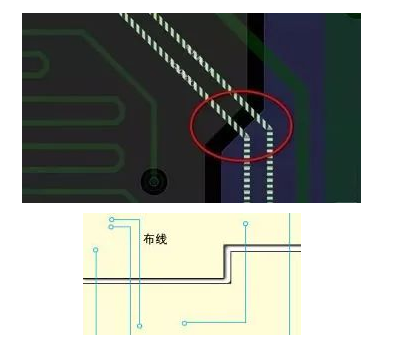

而且,通孔离微带线太近或者微带线下方的参考平面上有间隙,这都会增加信号回流路径的阻抗。从信号完整性的角度来看,在返回电流路径中阻抗增加等同于在信号迹线中阻抗增加。 间隙使得返回路径不连续性,改变了信号线的特性阻抗,从而导致信号波形的反射和失真,并再次导致更高的 EMI 和信号完整性的降低。

2022-11-15 14:55

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整

2022-02-12 10:41

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整

2020-09-02 11:06

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整

2023-03-09 09:27

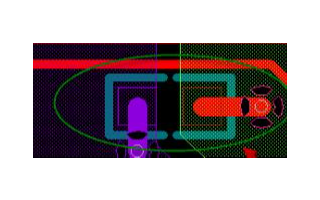

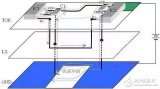

缝补电容Stiching Capacitor+通常在信号跨分割处摆放一个 0402 或者 0603封装的瓷片电容,电容的容值在 0.01uF 或者是 0.1 uF,如果空间允许,可以多添加几个?样的电容?同时尽量保证信号线在缝补电容 200mil 范围内,距离越小

2023-11-23 15:25

如果参考平面上有间隙,然后信号穿过该间隙,会在PCB中产生很多不良性能。

2022-11-16 14:16

我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地

2024-01-03 15:12

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整

2024-01-10 15:28

跨线桥接。常见的就是在信号层对跨分割的“信号包地处理”,也可能包的是其他网络的信号线,这个“包地线”要尽量粗。

2019-11-26 15:53