PCB 上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"

2020-10-30 14:39

由于 PCB 板的密度越来越高,许多 PCB LAYOUT 工程师在走线的过程中,较容易出现一种失误,即时钟信号等高速信号

2024-01-08 15:33

本文主要详解PCB设计高速模拟输入信号走线,首先介绍了PCB设计高速模拟输入信号

2018-05-25 09:06

在进行PCB布线时,经常会发生这样的情况:走线通过某一区域时,由于该区域布线空间有限,不得不使用更细的线条,通过这一区域后,线条再恢复原来的宽度。走线宽度变化会引起阻抗变化,因此发生反射,对

2020-01-01 17:35

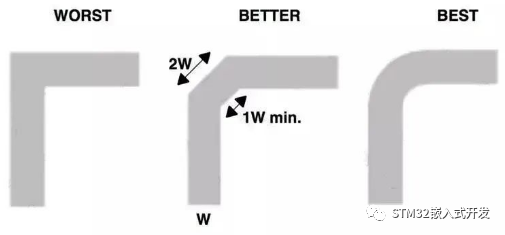

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走

2023-04-03 16:29

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有

2017-11-25 07:43

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏

2020-02-14 11:53

每次串行数据速率提高,其都会暴露出掩盖在低速下的问题。许多这些问题是因为PCB走线、过孔和连接器中发生损耗引起的信号完整性下降而造成的。

2018-02-05 19:16

PCB布线中的蛇形走线 PCB上的任何一条走线在通过高频

2009-09-13 15:15

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52