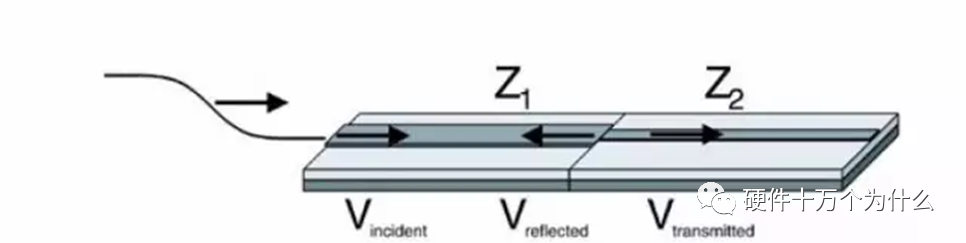

在进行PCB布线时,经常会发生这样的情况:走线通过某一区域时,由于该区域布线空间有限,不得不使用更细的线条,通过这一区域后,线条再恢复原来的宽度。走线宽度变化会引起阻抗变化,因此发生反射,对

2020-01-01 17:35

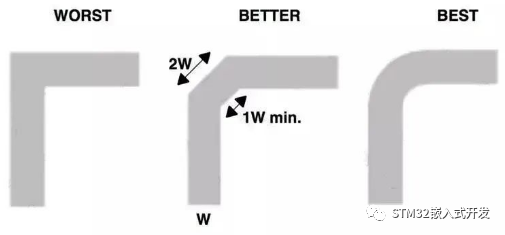

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走

2023-04-03 16:29

每次串行数据速率提高,其都会暴露出掩盖在低速下的问题。许多这些问题是因为PCB走线、过孔和连接器中发生损耗引起的信号完整性下降而造成的。

2018-02-05 19:16

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

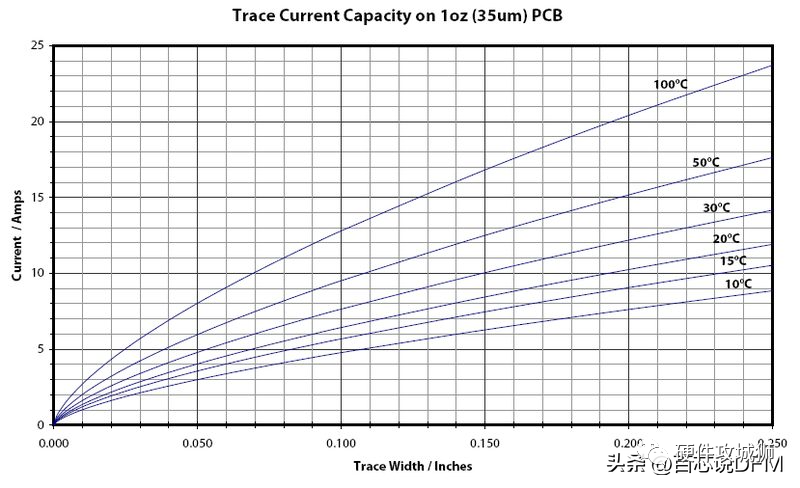

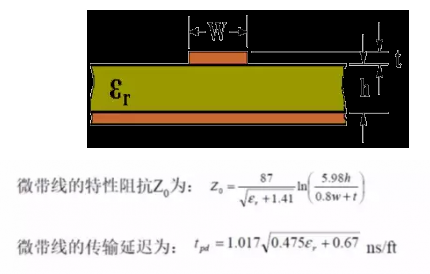

走线宽度是PCB设计中最关键的因素之一。

2023-07-12 13:53

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏

2023-05-22 09:15

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走

2019-06-06 14:43

由于电信号在PCB上传输,我们在PCB设计中,可以把PCB走线认为是信号

2023-07-25 14:13

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线

2019-10-04 17:17