电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4mil(或6mil),线间距不低于8mil;高密度板可采用4/6mil的线宽/间距,低密度版,尽量采用6/8mil的线宽/间距。

2019-10-25 14:16

在普通印制电路板的布线中由于信号是低速信号,所以在3W原则的基本布线规则下按照信号的流向将其连接起来,一般都不会出现问题

2019-03-24 10:00

如何优雅的布线呢?布线的方式可以千差万别,为了在布线时避免输入端与输出端的边线相邻平行而产生反射干扰和两相邻布线层互相平行产生寄生耦合等干扰而影响线路的稳定性,甚至在干

2018-07-28 11:01

双层pcb板正反两面都有布线,元器件可以焊接在正面,也可以焊接在反面,双层线路板这种电路板的两面都有元器件和布线,不容质疑,设计双层PCB板的难度要高更多,下面我们来分

2017-08-26 16:03

PCB板是重要的电子部件,是所有电子元器件的母体,从上世初开始出现到现在也变得越来越复杂,从单层到双层、四层,再到多层,设计难度也是不断增加。因为双层板正反两面都有布线,所以了解和掌握它的布线原则对于我们的设计是非常

2018-04-24 10:52

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

即相邻层的走线方向成正交结构。避免将不同的信号线在相邻层走成同一方向,以减少不必要的层间窜扰;当由于板结构限制(如某些背板)难以避免出现该情况,特别是信号速率较高时,应考虑用地平面隔离各

2019-05-31 16:20

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽

2023-05-22 09:15

布线非常靠近的差分信号对相互之间也会互相紧密耦合,这种互相之间的耦合会减小EMI发射,差分信号线的主要缺点是增加了PCB的面积,本文介绍电路板设计过程中采用差分

2017-12-11 15:47

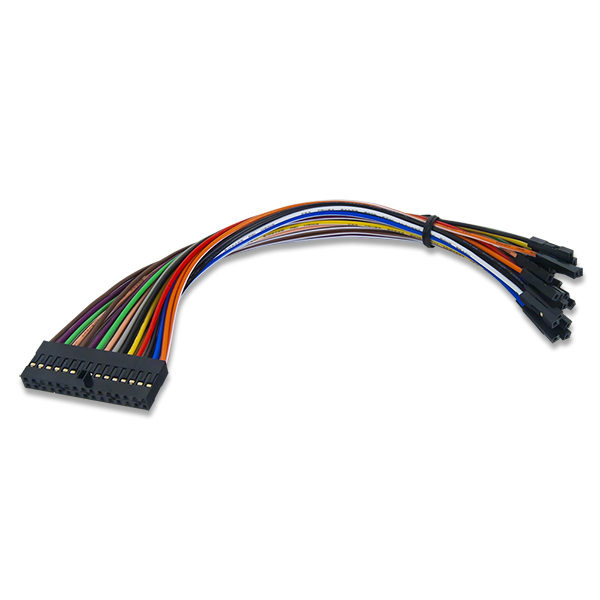

Analog Discovery信号线组件,或称Flywire,是与Analog Discovery产品原装信号线相同的组件。

2019-11-26 11:08