数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

PCB设计中常见的走线等长要求

2023-11-24 14:25

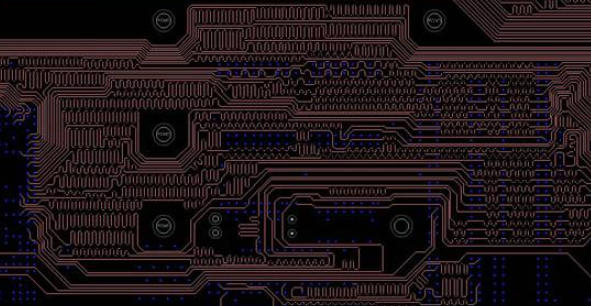

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

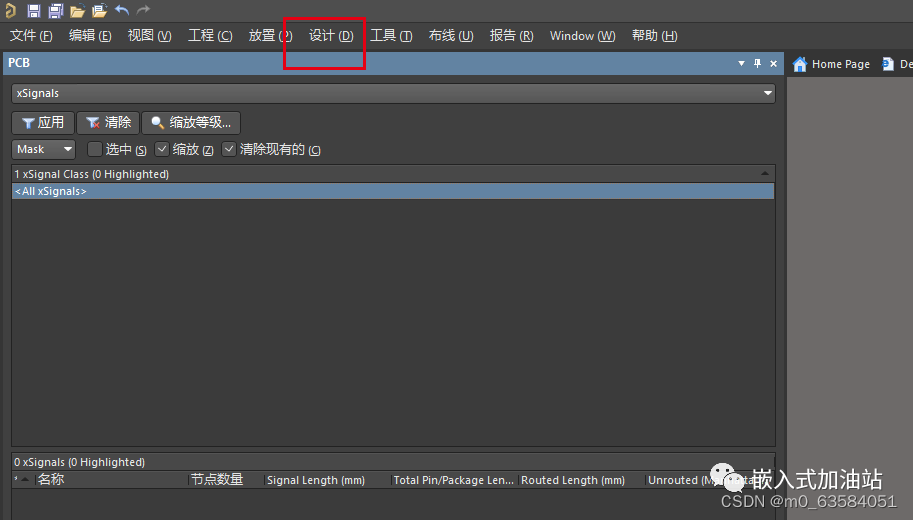

1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走

2023-07-27 07:40

挥不去的痛。需要等长设计的总线越来越多,等长的规则越来越严格。5mil已经不能满足大家的目标了,精益求精的工程师们开始挑战1mil,0.5mil……还听过100%等长,没有误差的要求。 为什么我们这么喜欢

2021-01-20 12:11

如图所示很多用户在进行等长的时候回出现直角或者锐角的等长走线。 那么怎么解决呢: 1)在直接快捷键TR进行蛇形等长的时候,可以按字母键盘上方的数字1 或者2来调整

2020-10-18 09:36

为了使二个SDRAM的时钟线等长,设置等长的方法有很多,在这里我们只为了二条时钟线等长来学习如何通过设置约束规则然后通

2010-06-21 11:57

等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27

至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟包含在数据中发出,数据接收方通过接收到的数据恢复出时钟信号。

2020-11-19 16:29