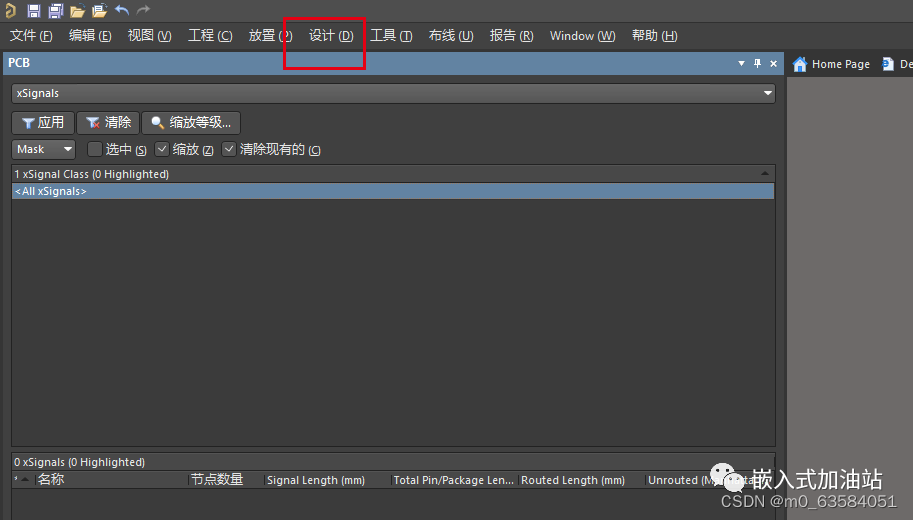

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition

2018-05-15 10:49

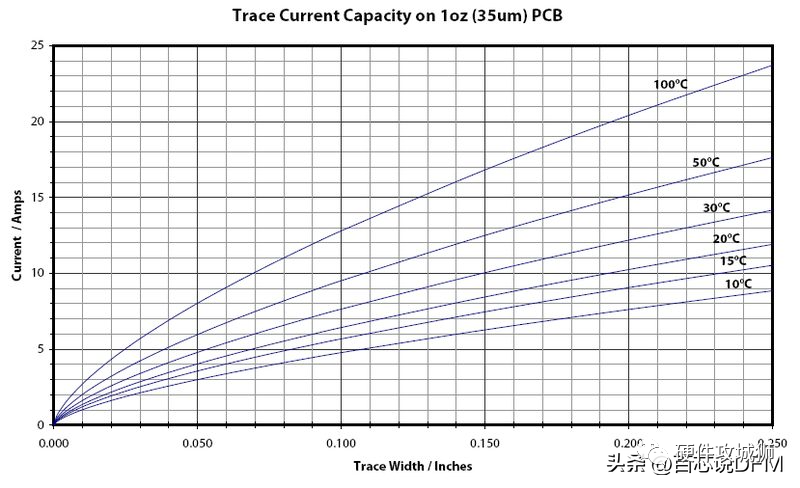

走线宽度是PCB设计中最关键的因素之一。

2023-07-12 13:53

当涉及到PCB 设计时,PCB 走线电流容量带来的限制是至关重要的。虽然IPC-2221通用设计指南是一个很好的起点,但 PCB

2022-08-22 09:05

数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线一侧是VCC,另一侧是GND,那么哪个是参考平面?

2018-03-08 17:18

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。

2019-03-19 17:30

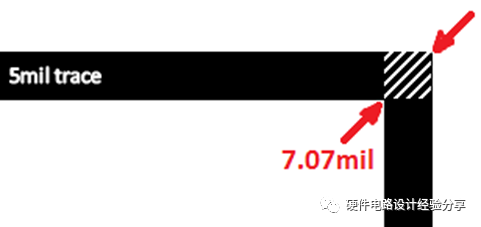

本期跟大家分享的是,为什么在PCB layout时不能走直角线?

2023-11-20 18:24

本文主要介绍的是pcb开窗,首先介绍了PCB设计中的开窗和亮铜,其次介绍了如何实现PCB走线开窗上锡,最后阐述了PCB设

2018-05-04 15:37

线宽要按50或者100欧姆设计,差分线要做等长,电源走线要粗一点,电源地平面最好紧耦合等等这些PCB设计的常规操作相信没人质疑。那么对于走线包地要打孔,估计你们也不会有

2021-03-29 11:46