说到扩容,不少人的第一反应都是解决比特币拥堵问题的闪电网络(Lightning Network),和其以太坊版本的雷电网络(Raiden Network)。由于这两种解决方式是对公链本身性能的补充,因此我们暂不把它们算作中间层,本文仅做简单介绍。

2018-08-20 16:51

实际的应用中,DFN3*3、DFN5*6、SO8等封装类型的贴片元件,都会在PCB板器件位置的底部铺上一大片铜皮,然后器件底部框架的铜皮焊接在PCB的这一大片的

2023-02-16 11:13

本文为您讲述PCB铜皮作为导线通过大电流,铜箔厚度(三种规格35um、50um、70um)不同宽度下载流量的参考数值,具体对照表及PCB电路板铜皮宽度和所流过电流量大小

2016-09-21 17:04

有线门磁为嵌入式安装更加隐蔽,感应门窗的开合,适用于木质或铝合金门窗发出有线常闭/常开开关信号。门磁是用来探测门、窗、抽屉等是否被非法打开或移动。它由无线发射器和磁块两部分组成。门磁系统其实和床磁等原理相同。

2018-10-07 11:49

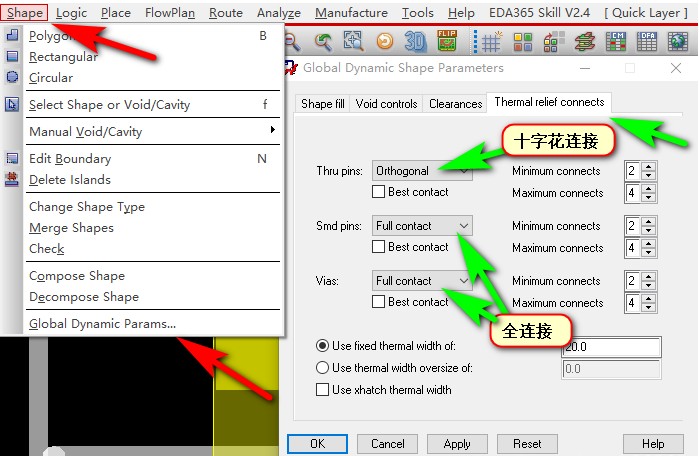

在PCB常规设计下,整板铜皮与焊盘的连接方式已经在Sbapa菜单栏下的Global Dynamic Shape Parameters选项下的Thermal relief connect选项栏中已经设置好了

2019-10-27 12:31

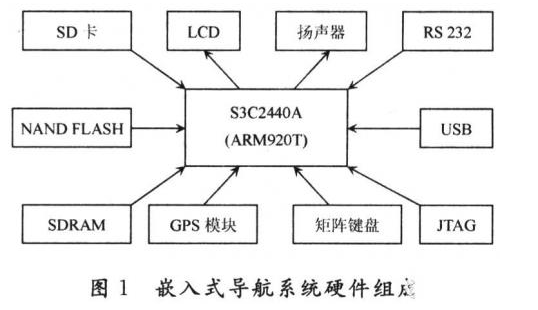

嵌入式导航系统由硬件层、软件层和中间层组成。

2020-01-08 09:15

相比于仅使用logits的蒸馏方法,同步使用模型中间层特征进行蒸馏的方法通常能取得更好的性能。然而在异构模型的情况下,由于不同架构模型对特征的不同学习偏好,它们的中间层特征往往具有较大的差异,直接将针对同架构模型涉及的蒸馏方法迁移到异构模型会导致性能下降。

2023-11-01 16:18

在PCBLayout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。

2019-09-17 14:22

在Cadence Allegro16.6版本中,可以很方便的对Shape铜皮进行外扩或者内缩,而不需要重新绘制。

2018-12-02 11:16

Allegro中如何合并铜皮,这又是一篇有关Allegro操作的简短文章,同样是近期很多读者搜索的。Allegro中简单快捷的绘制Shape的操作,是我非常喜欢Allegro的一个原因,使用者可以轻易地绘制出各种需要的Shape。

2019-06-08 14:32