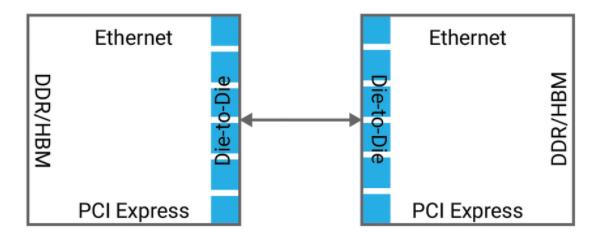

本文介绍了 die-to-die 连接的几种不同用例,以及在寻找用于 die-to-die 连接的高速 PHY IP 也可以使用基于有机基材的传统低成本封装。

2020-05-18 09:57

在半导体行业中,“die”,“device”,和“chip”这三个术语都可以用来指代芯片。

2024-02-23 18:26

Wafer、die、chip是半导体领域常见的术语,但是为什么单颗裸芯会被称为die呢?

2024-01-24 09:14

2D芯片设计中通常为二阶或三阶的效应,在Multi-Die系统中升级为主要效应。

2023-12-19 17:24

Multi-Die设计是一种在单个封装中集成多个异构或同构裸片的方法,虽然这种方法日益流行,有助于解决与芯片制造和良率相关的问题,但也带来了一系列亟待攻克的复杂性和变数。尤其是,开发者必须努力确保

2025-02-25 14:52

芯砺智能近日宣布,其全自研的Chiplet Die-to-Die互连IP(CL-Link)芯片一次性流片成功并顺利点亮。这一重大突破标志着芯砺智能在异构集成芯片领域取得了领先地位,为人工智能时代的算力基础设施建设提供了更加多元灵活的互连解决方案。

2024-01-18 16:03

在高速PCB设计中,往往需要采用多层PCB,而过孔是多层PCB 设计中的一个重要因素。

2022-11-10 09:08

小芯片针对每个功能组件进行了优化。虽然Multi-Die系统具有更高的灵活性并在系统功耗和性能方面表现优异,但也带来了极高的设计复杂性。 通用芯粒互连技术(UCIe)标准于2022年3月发布,旨在推动Multi-Die系统中

2023-07-14 17:45

Multi-Die系统的基础构建,亦是如此,全部都需要细致入微的架构规划。 对于复杂的Multi-Die系统而言,从最初就将架构设计得尽可能正确尤为关键。 Multi-Die系统的出现,是为了应对设计规模增加和系统复

2023-09-22 11:07

一文带你了解PCB中的金手指

2019-08-14 16:38