在一个电路系统中, 时钟是必不可少的一部分。如人的心脏的作用,如果电路系统的时钟出错了,系统就会发生紊乱,因此在PCB 中

2020-08-01 11:41

在 PCB 设计中,您希望时钟信号迅速到达其集成电路( IC )的目的地。但是,一种称为时钟偏斜的现象会导致时钟信号早晚

2020-09-16 22:59

布局 时钟晶体和相关电路应布置在PCB的中央位置并且要有良好的地层,而不是靠近I/O接口处。不可将时钟产生电路做成子卡或者子板的形式,必须做在单独的时钟板上或者承载板上

2018-02-20 20:26

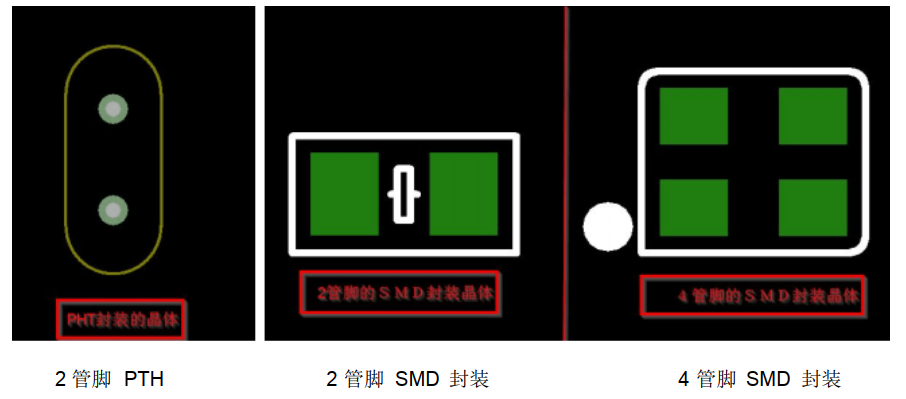

布局、布线总结: 滤波电容靠近电源管脚,遵循先大后小原则摆放,小电容靠得最近; 匹配电阻靠近晶振摆放;如果原理图中没有这个电阻,可建议加上; 时钟线按 50 欧姆阻抗线来走;如果时钟线过长,可以走在内层,打孔换层处加回流地孔;

2023-11-13 11:35

在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功

2024-01-11 09:50

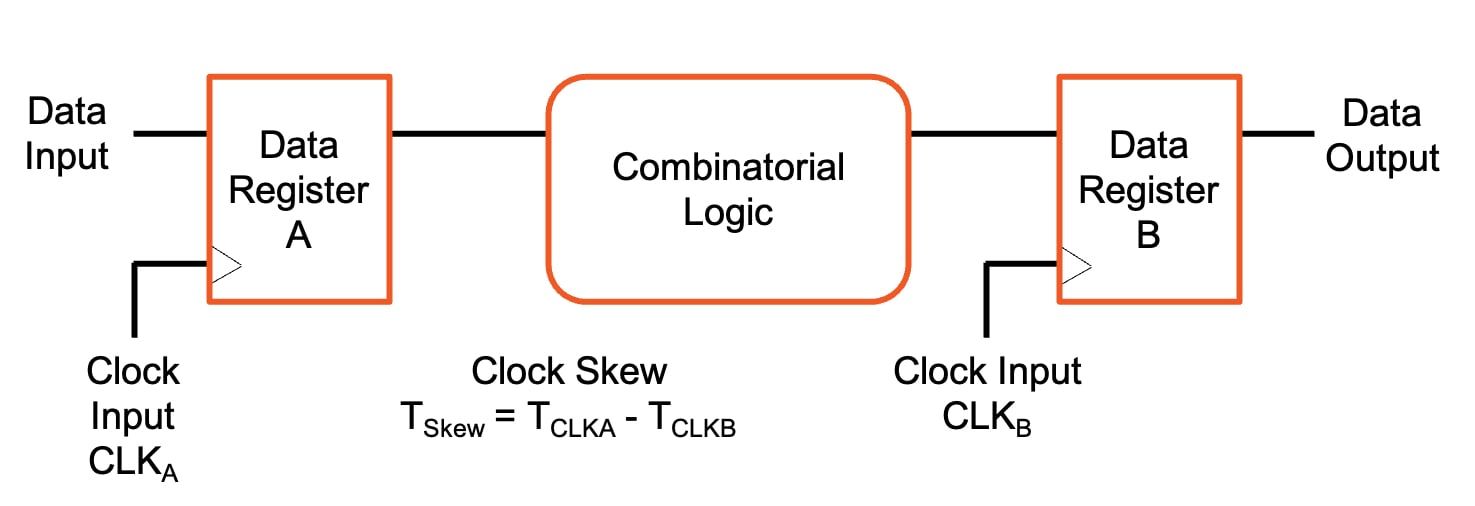

字电路中具有控制良好、定义明确的时序。 时钟偏斜 是这些电路中的一个设计考虑因素,如果不适当考虑,可能会成为重要的故障来源。事实上,在许多情况下,系统的时钟偏差可能是整

2023-01-27 10:05

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计

2020-11-23 13:08

数字设计中的时钟与约束 本文作者 IClearner 在此特别鸣谢 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的

2023-01-28 07:53

时钟晶体和相关电路应布置在PCB的中央位置并且要有良好的地层,而不是靠近I/O接口处。不可将时钟产生电路做成子卡或者子板的形式,必须做在单独的时钟板上或者承载板上。

2023-02-08 09:12