生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功

2024-01-11 09:50

数字设计中的时钟与约束 本文作者 IClearner 在此特别鸣谢 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的

2023-01-28 07:53

大型时钟树通过多个时钟设备、使用多种传输线类型以及跨多个板和同轴电缆路由时钟信号的情况并不少见。即使遵循最佳实践,这些介质中的任何一种都可能引入大于 10 ps 的

2022-12-22 15:19

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚

2020-11-22 11:54

今天我们讲一下与时钟(clock)相关的PCB的设计考虑,主要分两部分:原理图设计 - 针对时钟电路应该放置哪些器件?以及PCB布局和走线 - 如何摆放与

2018-11-25 11:09

线宽要按50或者100欧姆设计,差分线要做等长,电源走线要粗一点,电源地平面最好紧耦合等等这些PCB设计的常规操作相信没人质疑。那么对于走线包地要打孔,估计你们也不会有什么意见吧…… 有些PCB

2021-03-29 11:46

在一个SOC设计中,存在多个、独立的时钟,这已经是一件很平常的事情了。大多数的SOC器件都具有很多个接口,各个接口标准都可能会使用完全不同的时钟频率。

2017-02-11 15:07

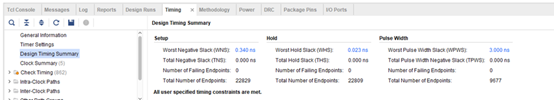

本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟

2022-08-02 11:44

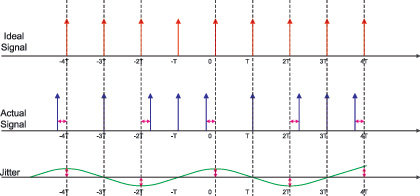

同步模块是每个系统的心脏,它为系统中的其他每个模块馈送正确的时钟信号。因此需要对同步模块的设计和实现给予特别关注。本文对影响系统设计的时钟特性进行了考察,

2006-03-11 13:21

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-03-15 14:05