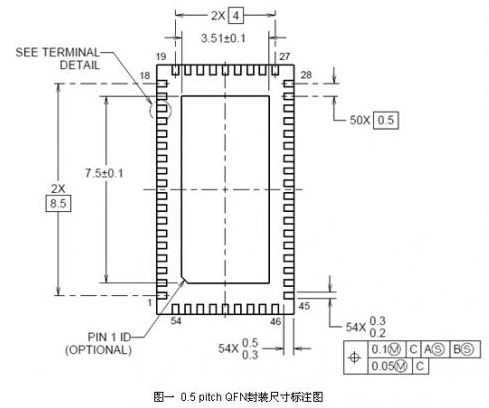

在PCB设计中,QFN封装的器件通常使用微带线从TOP或者BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。

2019-10-04 17:09

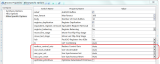

该属性会将每个驱动程序的扇出限制告知工具,并通过指示布局器了解扇出限制来指引该工具对高扇出的负载进行分配。此属性可同时应用于 FF 与 LUT 驱动程序。当 MAX_FANOUT 值小于约束的信号线的实际

2025-08-28 10:47

高扇出信号线 (HFN) 是具有大量负载的信号线。作为用户,您可能遇到过高扇出信号线相关问题,因为将所有负载都连接到 HFN 的驱动程序需要使用大量布线资源,并有可能导致布线拥塞。鉴于负载分散,导致进一步增大信号线延迟,因此在高

2025-08-28 10:45

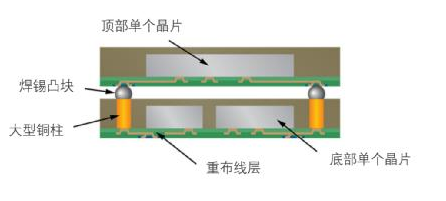

扇出型封装一般是指,晶圆级/面板级封装情境下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。扇出型封装的核心要素就是芯片上的RDL重布线层(可参考下面图表说明

2023-11-27 16:02

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17

Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化

2019-10-13 14:55

Xilinx推荐对于低扇出的触发器控制信号在代码编写时尽量吸收进触发器D输入端之前的LUT中,并在XST的综合属性选项中提供配置项,让XST综合时自动将低扇出的控制信号吸收进触发器D输入端之前的LUT

2023-12-14 15:04

高密度扇出型封装技术满足了移动手机封装的外形尺寸与性能要求,因此获得了技术界的广泛关注。

2020-07-13 15:03

一文带你了解PCB中的金手指

2019-08-14 16:38

RDL 技术是先进封装异质集成的基础,广泛应用扇出封装、扇出基板上芯片、扇出层叠封装、硅光子学和 2.5D/3D 集成方法,实现了更小、更快和更高效的芯片设计。

2024-03-01 13:59