小间距QFN封装PCB设计串扰抑制分析

2022-11-04 09:51

电子发烧友网为你提供PCB设计的串扰问题解决资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-28 08:42

高速PCB 串扰分析及其最小化乔 洪(西南交通大学 电气工程学院 四川 成都 610031)摘要:技术进步带来设计的挑战,在高速、高密度PCB 设计中,

2009-12-14 10:55

如果您给某个传输线的一端输入信号,该信号的一部分会出现在相邻传输线上,即使它们之间没有任何连接。信号通过周边电磁场相互耦合会产生噪声,这就是串扰的来源,它将引起数字系统的误码。一旦这种噪声在相邻

2020-10-10 10:43

2015-05-13 17:36

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串

2020-11-02 09:19

双绞线的性能在一直不断的提高,但有一个参数一直伴随着双绞线,并且伴随着双绞线的发展,这个参数也越来越重要,它就是串扰 (Crosstalk)。串扰是影响数据传输最严重的

2018-01-19 11:15

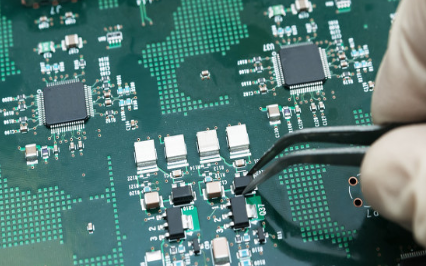

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出

2022-11-21 06:14

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,

2019-04-18 09:30

间耦合以及绕线方式等有关。随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,

2015-01-05 11:02