在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

2020-10-24 09:29

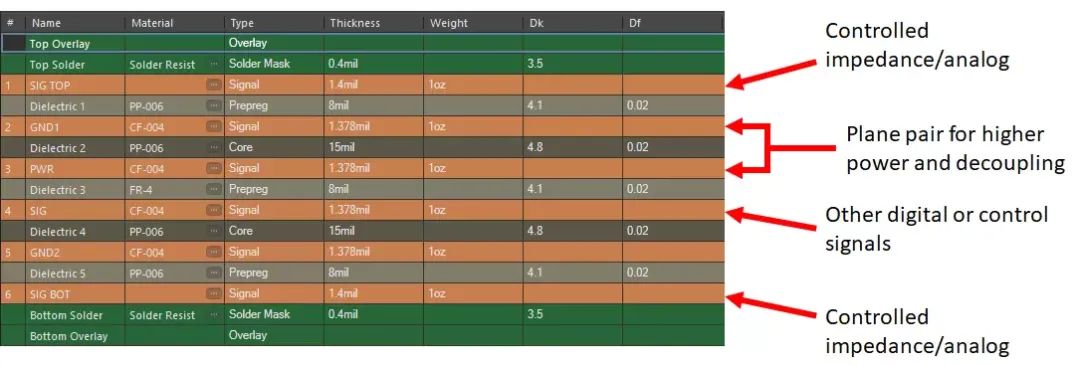

4层PCB上的空间用完后,就该升级到6层电路板了。额外的层可以为更多的信号、额外的平面对或导体的混合提供空间。如何使用这

2023-10-16 15:24

多年来,多层 PCB 在各个行业中都获得了极大的普及。如今,很容易找到几种类型的多层 PCB ,包括 4 层 PCB , 6

2020-09-18 23:35

PCB设计中常见的走线等长要求

2023-11-24 14:25

经常画高速板的同学都知道,10个高速板有9个要绕等长,而且内存出现的频率尤其频繁,整的现在画板子不绕两下都有点不习惯。好在上期给大家介绍了几种快的不能再快的绕等长的方法,用allegro绕等长还是非常任性的。看看下图

2018-11-11 10:55

1.关于等长 第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。 不知道从什么时候起,绕等长成了一种时尚,也成了

2021-01-20 12:11

等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27

6 层板堆叠在 PCB 设计中的重要性 数十年来,多层印刷电路板一直是设计领域的主要内容。随着电子元件的缩小,从而允许在一块板上设计更多的电路,它们的功能增加了对支持它们的新型

2020-09-14 01:14

在PCB设计中,对于消费类电子或者一些对成本要求比较高的PCB板,为了成本的降低,多采用6层板设计,而器件布局空间上也是比较紧张的,这就对叠

2020-05-12 16:19

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是

2019-03-19 17:30