刚接触Linux,认为直接make后就完成了编译,没想到编译出的结果存在很大问题,原来是make、make all和make clean的使用方法不对。

2024-01-05 12:32

点击右键选择设置群原点(Set Group Origin),鼠标左键点击,设置群原点的地方。以后在打开这个重复使用电路时,光标将依附在设置的群原点的地方。这主要是为了后续对产生的Reuse模块进行精确定位。

2019-01-15 17:20

EDA软件中allegro的模块复用非常实用,可能通常我们的工程师还用的不多,但它在某些场合下还是很有用的,一个是它能减少我们重复性的工作,可以重用的原理图和PCB我们就不需要重复设计了,也就是REUSE。

2018-07-15 10:16

在PADS logic 中原理图同步PCB

2019-09-22 10:41

在《Reuse methodology manual》第五章,主要收集了一些HDL代码的规范和指导。遵照这些规范或者指导的目的是让你的代码更加的具有可读性、可修改性、可重用;这个应该是所有语言所追求的;而针对HDL代码,还要使代码适合综合和仿真。

2017-02-11 13:23

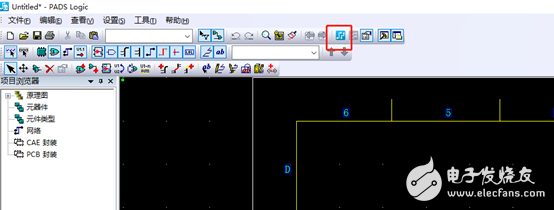

PADS Layout和Router同步模式在PADS 9.1 中已经可以通过点击工具栏的按钮在PADS Layout和PADS Router之间任意切换。

2019-11-22 15:01

CMake和Make是构建软件,其工作涉及将源代码转换为可执行程序。CMake和Make是旨在实现构建过程自动化的工具,帮助开发者节省时间和精力。

2024-02-27 11:44

pads原理图转换Altium Designer格式的图示 1、在powerlogic使用file下的export功能导出.txt文件。 2、格式选择为.txt,点击保存。 3、点击

2018-05-11 11:42

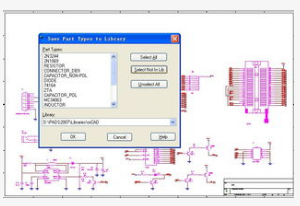

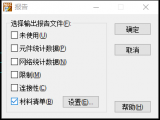

PADS Logic导出Layout网表的步骤教程,具体的跟随小编一起来了解一下。

2018-07-24 10:41

这里我们主要介绍PADS LOGIC里的Tools》options对话框中的General,在PADS2007中对原理图的操作这篇中,我们认识了原理图零件,在PCB LAYOUT画原理图之前,还有一个重要环节要了解,那就是下图

2011-11-11 17:50