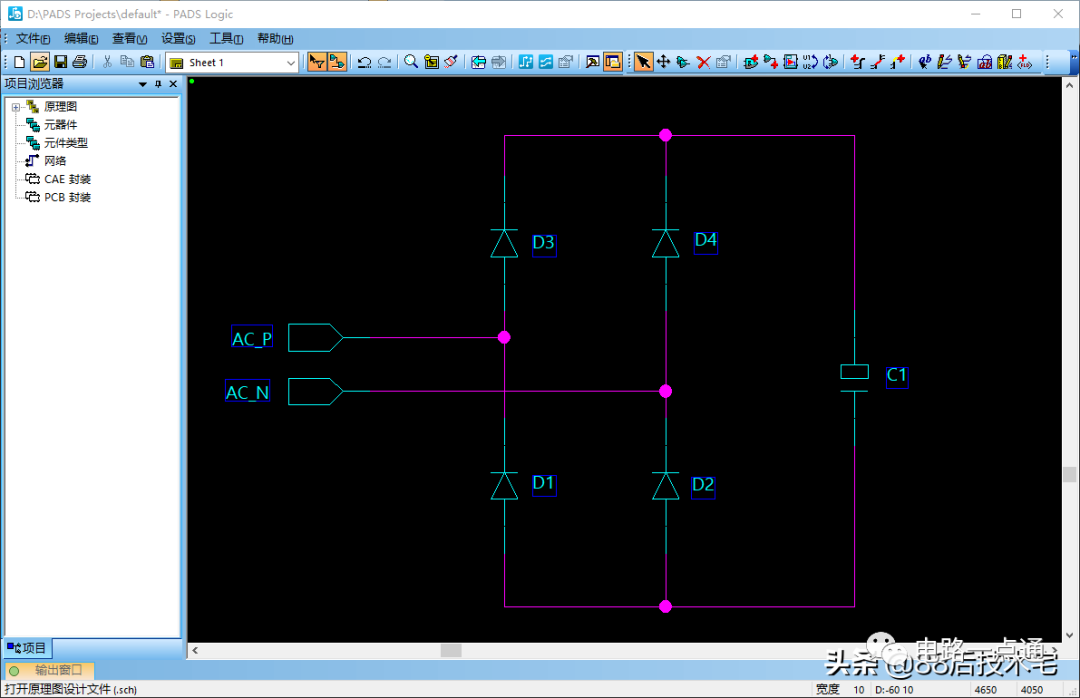

PADS Logic导出Layout网表的步骤教程,具体的跟随小编一起来了解一下。

2018-07-24 10:41

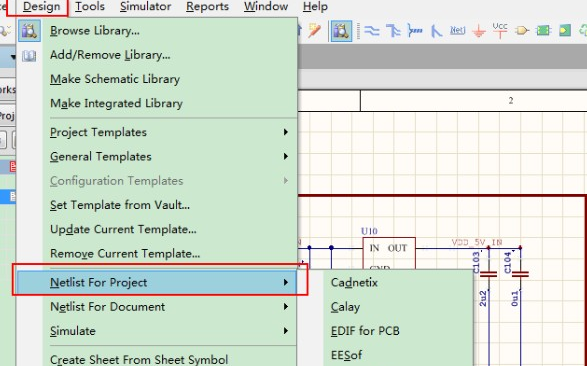

本文,主要描述了,如何使用Altium Desginer 导出Cadence可以使用的网表

2019-10-13 09:15

AltiumDesigner不需要网表导入导出这一操作,原理图画好后直接转入PCB非常方便。PADS就麻烦些,需要从原理图导出

2023-08-03 09:11

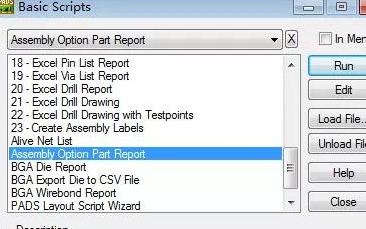

首先,我们需要了解脚本中的原理。在PADS导出BOM的脚本中,一般会读取元器件的相关信息,如元器件编号、名称、数量等。我们需要在脚本中增加元器件层信息的读取,以及在整理元器件时对层信息进行判断,从而实现元器件分顶层和底层的归类统计。

2023-09-23 09:24

在实际操作中,我们可能会遇到设计电脑使用的PADS layout版本低于PADS9.5版本,那么这时需要导出设计图时就要选择兼容低版本的文件。

2018-04-30 16:21

将左侧“Part Properties”中需要的条目“Add”到右侧的“Table Columns”中,右侧的条目就是导出BOM后Excel表格中显示的条目。

2019-08-30 10:25

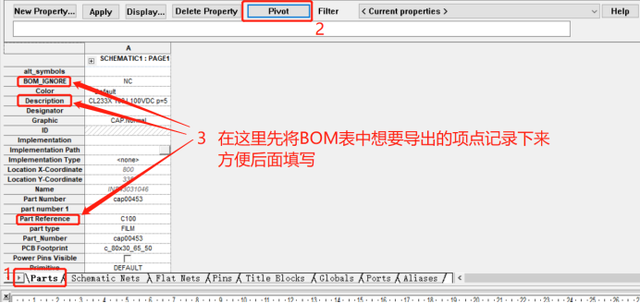

首先打开需要的Cadence 原理图文件,在原理图中任意选择一个器件双击,在弹出的对话框中,将BOM表中想要导出的项点提前记录下来(一般导出的BOM表中,会包含序号、物

2023-03-24 15:47

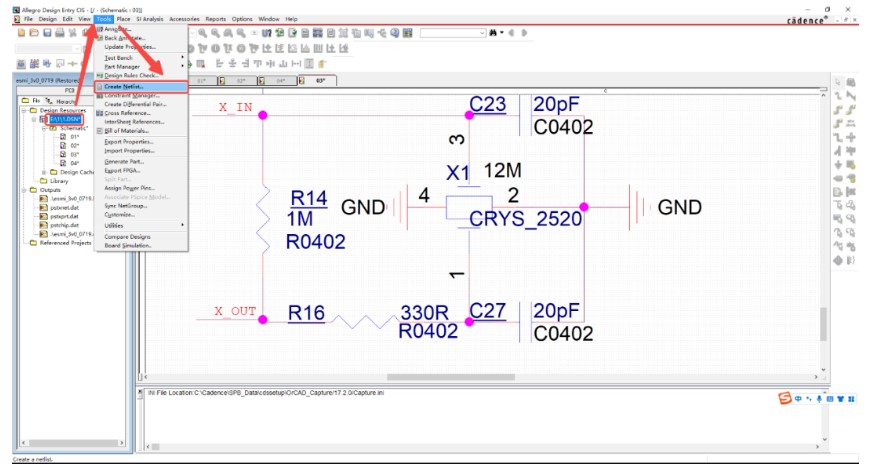

首先确定原理图设计OK,包括PCB封装、位号等规则检查等,先是点击工程名,然后在OrCAD的菜单栏下选择Tools,点击Create Netlist(产生网表)。

2022-09-23 09:06

用PADS9.2 LAYOUT打开文件,选择Export导出,导出格式Format选择PowerPCB V3.0的,然后Select All,还有Parts和Nets都选上。然后

2011-11-21 15:09

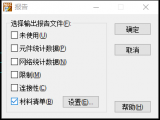

pads原理图转换Altium Designer格式的图示 1、在powerlogic使用file下的export功能导出.txt文件。 2、格式选择为.txt,点击保存。 3、点击

2018-05-11 11:42