密排六方的位错类型,根据伯氏矢量方向与C轴夹角可分为a位错、c位错、c+a位错。在此,为了能快速理解并分析,整理了两个问题,希望能帮助到大家。

2023-11-25 09:57

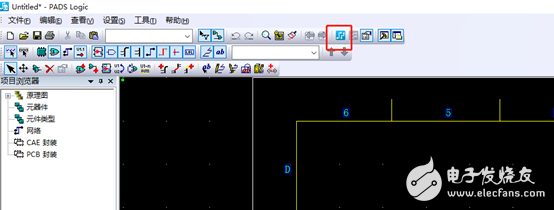

在PADS logic 中原理图同步PCB

2019-09-22 10:41

PADS Layout和Router同步模式在PADS 9.1 中已经可以通过点击工具栏的按钮在PADS Layout和PADS Router之间任意切换。

2019-11-22 15:01

设含位错的晶体为简单立方晶体,在其晶面ABCD上半部存在多余的半排原子面EFGH,这个半原子面中断于ABCD面上的EF处,它好像一把刀刃插入晶体中,使ABCD面上下部分晶体之间产生了原子错排,故称为“刃型位错”,多余

2023-12-02 11:40

位错密度为单位体积内位错线的总长度,其数学表达式

2023-12-09 10:38

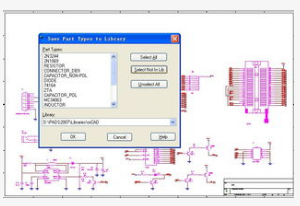

pads原理图转换Altium Designer格式的图示 1、在powerlogic使用file下的export功能导出.txt文件。 2、格式选择为.txt,点击保存。 3、点击

2018-05-11 11:42

最近收到老师同学们的许多问题,其中大家最想要了解的问题是“如何在透射电镜下判断位错类型(螺位错、刃位错、混合位错)”。在此,为了能快速理解并分析,我整理了三个问题,希望

2023-11-13 14:37

概述PADS是业界应用最普遍的电子设计解决方案,其中涵盖了原理图设计、模拟仿真、PCB布局布线设计、信号和电源完整性分析(SI/PI)、热分析、可制造性分析等全套的功能需求。PADS还兼容其他同类

2025-11-17 10:39 深圳市和粒科技有限公司 企业号

位错在晶体中的存在,使其周围原子偏离平衡位置,而导致点阵畸变和弹性应力场的产生。

2023-12-22 16:22

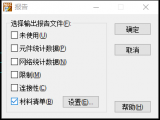

PADS Logic导出Layout网表的步骤教程,具体的跟随小编一起来了解一下。

2018-07-24 10:41