分线,千兆模式下是4对差分线。在部分PHY芯片的Datasheet或者应用手册中会给出MII/RMM/GMII/RGMII接口,MDI接口的等长规则,但是很少有厂家提到以太网变压器与RJ45之间的差分对等长规则。

2019-05-26 09:38

在DDR的PCB设计中,一般需要考虑等长和拓扑结构。等长比较好处理,给出一定的等长精度通常是PCB设计师是能够完成的。但对于不同的速率的DDR,选择合适的

2017-11-08 13:00

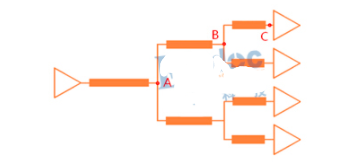

T拓扑本身就是一堆的阻抗不连续,反射不仅存在于每个分支内部,还会在分支之间影响,因此各分支接收端的波形会有比较大的反射振铃。

2021-04-11 10:07

1.将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要

2018-05-22 10:45

按照上面的操作来做等长是不是可以更准一点,给DDR4系统留取更多的裕量呢?由于李工的项目最根本原因不是等长,而是由于他使用了多颗粒双die DDR4表底贴设计,阻抗和拓扑结构优化不到位导致(这种设计在我司的定位难度级

2022-09-13 17:08

有了单线的自动等长,那就肯定不会放过板上随处可见的差分了,看大招——Auto-interactive Phase Tune。现在板子的速率越来越高,板上的差分线也就跟着越来越多,对内等长的工作量自然就加大了。但是自从有了绕线新功能,就再也不担心绕

2018-10-19 15:33

在绘制原理图元件的时候,有时管脚数量过多,管脚编号会显的特别密。既可以选择隐藏管脚编号,显示主要目的就是分辨出信号管脚。 第一步:在创建元件界面,执行菜单命令设置-显示

2023-07-14 07:35

如图所示很多用户在进行等长的时候回出现直角或者锐角的等长走线。 那么怎么解决呢: 1)在直接快捷键TR进行蛇形等长的时候,可以按字母键盘上方的数字1 或者2来调整等长走

2020-10-18 09:36

探讨 PADS Standard 和 PADS Standard Plus 所包含的功能。PADS Standard 可满足专注于原理图和 PCB 设计的工程师的需求。PADS

2019-05-15 06:03

PADS2007如何使用PADS2005中的元件封装库 装了PADS2007想用以前的PADS2005的库.发现不行...做了几个封装后不甘心...看有没有别的

2007-11-08 10:31