老电工李师傅是一名从事电工行业多年的资深工程师,他说:“有些电器故障是可以自己解决的,比如说空开和漏保故障,只要我们了解它们的特点,就能够快速判断问题所在。”

2023-05-22 10:38

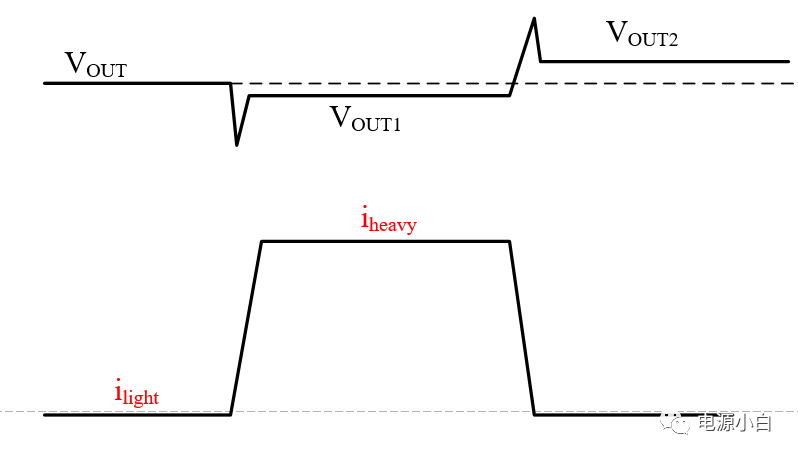

我们知道,在LDO或者开关变换器里,VIN(输入电压)以及i(负载电流)的突变会引起VOUT(输出电压)的瞬态变化,引起overshoot(过冲)或undershoot(下冲)的现象。当然,这和电路本身的带宽有关。这里仅以LDO为例,快速判断VOUT的变化方向。

2023-11-07 17:29

在判断变频器好坏前,拆除掉电源进线和负载出线,拆完只需15秒就可以判断变频器好坏。

2020-12-05 17:41

CPU异常是较为常见且影响较大的问题之一。本文将从多个方面探讨如何快速判断PLC出现问题时是否为CPU异常,并提供相应的解决方法和建议。

2024-06-12 11:13

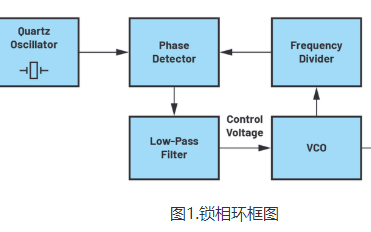

在PLL和VCO频率合成系统中,获得低于5 µs的频率和相位建立时间需极宽的环路带宽。环路带宽(LBW)定义控制环路的速度。更宽的LBW允许更快的建立时间,但会牺牲相位噪声和杂散信号的衰减能力。

2016-07-20 16:15

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2020-10-06 14:43

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14