随着英特尔Alder Lake CPU的发布,以及AMD 7000 Ryzen CPU的即将发布,PCIe 5.0 硬件终于成为现实。但什么是 PCIe 5.0?

2023-11-18 16:48

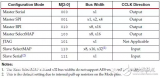

该信号为全局复位信号,由处理器系统提供(RC),处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设

2018-12-22 14:45

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相应的控制信号,例如PCIe配置空间和IP相干的配置信号。

2024-02-26 18:19

根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspc

2018-06-19 10:24

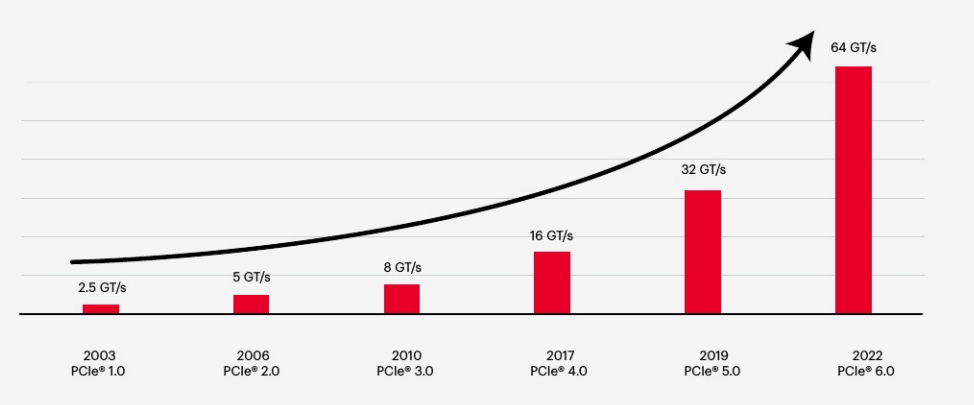

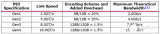

自2003年推出以来,PCIe发展至今已经从最初的1.0升级到了6.0,本文则为大家简单介绍一下PCIe标准的演进历史以及各代PCIe标准之间的主要差异。

2023-12-14 16:38

硬盘是大家都很熟悉的设备,一路走来,从HDD到SSD,从SATA到NVMe,作为NVMe SSD的前端接口,PCIe再次进入我们的视野。作为x86体系关键的一环,PCIe标准历经PCI,PCI-X

2021-01-09 10:41

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而

2017-12-12 10:37

PCIe总线错误检测囊括了链路(Link)上的错误以及包传递过程中的错误,如下图所示。用户设计的应用程序层中的错误不属于链路传输中的错误,不应当通过PCIe的错误检测与处理机制处理,一般可借助设备特殊中断(Device Specific Interrupt)等合适

2018-08-18 11:05

CPU 发起的,访问PCIe设备配置空间的数据流。这种数据流主要是BIOS/Linux PCIe driver 对设备进行初始化、资源分配时,读写配置空间的。包括PCIe 枚举,BAR 空间分配

2023-09-15 09:39

AMD FPGA自带PCIE硬核,实现了PCIE协议,把串行数据转换为并行的用户数据

2023-07-14 15:53