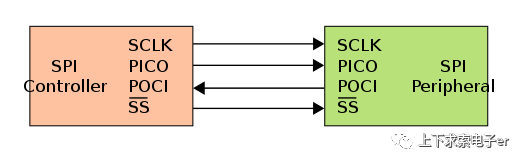

串行外设接口(Serial Peripheral Interface)的简称也叫做SPI,是一种高速、全双工同步通信的一种接口,串行外设接口一般是需要4根线来进行通信(NSS、MISO、MOSI

2023-10-26 14:26

。配置GPIO片选,推挽输出,上拉;SCLK、MOSI、MISO所用到的引脚为复用功能;SCLK下拉,MOSI推挽复用,MISO无推挽。下面我们来看看具体程序设计实现吧

2018-01-15 16:51

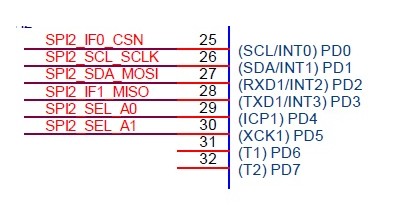

//spi标志 #define DDR_SPI DDRB #define DD_MOSI 5 #define DD_MISO 6 #define DD_SCK 7 #define DD_SS 4 #define CE PB3

2019-01-14 14:54

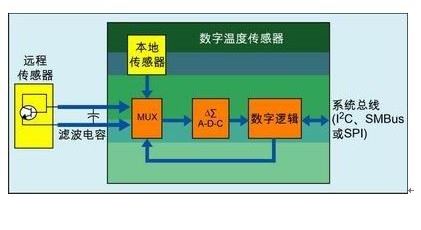

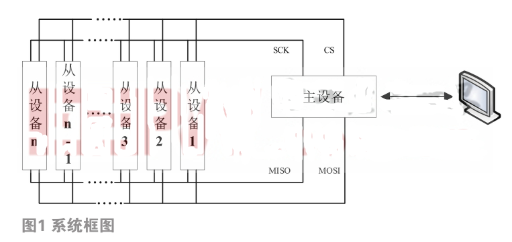

SPI 是一种四线制串行总线接口,为主/从结构,四条导线分别为串行时钟(SCLK)、主出从入(MOSI)、主入从出(MISO)和从选(SS)信号。主器件为时钟提供者,可发起读从器件或写从器件操作

2019-05-14 15:16

系统建立起来后,下一步是最终的板级验证。图6为用Chipscope得到的波形图。mosi与miso分别是发送端与接收端SPI总线上的信号。从图中可以看出数据基本吻合,由此表明设计的以FPGA控制NRF905的无线通信系统能够正常工作。

2018-08-26 09:34

CSN(IF0)、SCLK(SCL)、RSTN、MOSI(SDA)、MISO(IF1)、AC0(GPIO0)、AC1(GPIO1)(这些管脚中的RSTN、AC0、AC1由FPGA控制),括号内是管脚

2018-12-06 15:28

介绍SPI总线由开发,是一种,由四个IO口组成:CS、SCLK、MISO、MOSI;通常用于CPU和外设之间进行通信,常见的SPI总线设备有:TFTLCD、QSPIFLASH、时钟模块、IMU等

2025-02-26 19:00 RT-Thread官方账号 企业号

SPI数据总线只占用3或4个I/O(Master Output Slave Input,MOSI; Master InputSlave Output, MISO;Serial Clock,SCK;Chip Select,CS)端口,可以简化电路设计,节省端口资源,

2020-07-14 17:50