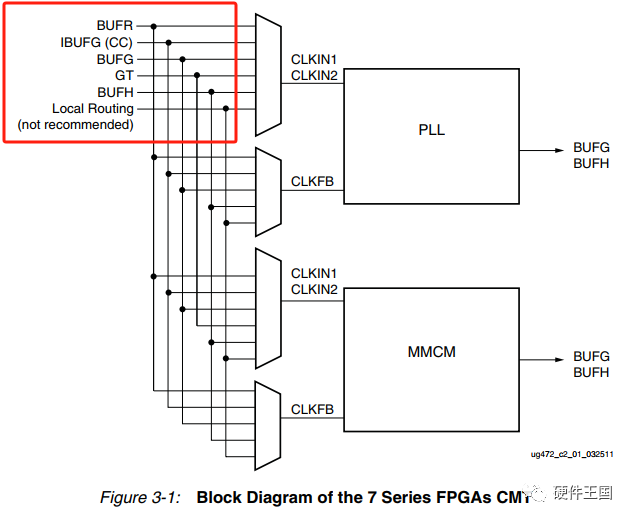

7系列FPGA包含最多24个CMT块,CMT具体的分布和与其他时钟资源的关系请参考本合集(FPGA应用开发)的上一篇文章。本文主要介绍CMT内部MMCM和PLL的区别以及在实际开发中怎么使用CMT,怎么实现跨时钟区域,第一次读者最好先阅读上一篇文章——解剖时钟结构篇。

2023-11-17 17:08

。通常的相位对齐技术由于引入了Delay_Aligner,会带来2~4nS的相位不确定,不能满足系统指标要求。 这里介绍一种利用MMCM实现多芯片相位对齐的串行收发器纠偏方法: 1) 利用图1所示电路实现多芯片间的全局时钟相位对齐。

2018-01-12 05:53

本文介绍了ADV7282A主要特性,功能框图,应用电路以及评估板EVAL-ADV7282AEBZ主要特性,连接图和电路图。

2018-06-17 18:33

ADV7183是一种综合视频解码器。它能够自动将一种兼容国际标准NTSC 或PAL的模拟视频基带信号转换成另一种兼容16位/8位CCIR601/CCIR656 的 YCrCb 型4:2:2或4:1

2021-03-17 09:34

ADV7513是一款165 MHz高清晰度多媒体接口(HDMI®)发射器,非常适合DVD播放器/录像机,数字机顶盒,A / V接收器,游戏机和PC。

2021-03-18 13:49

Discrete Jitter是由MMCM/PLL引入的,其具体数值可通过点击图2中Clock Uncertainty的数值查看,如图5所示。通常,VCO的频率越高,引入

2018-11-12 14:40

双击eclipse-inst-jre-win64安装包后按照如下截图进行配置

2023-04-15 10:15

本电路由一个数模视频转换器与一个低成本、低功耗、全集成式重构视频滤波器配合组成。ADA4430-1和ADV7393均推荐用于汽车领域,非常适合信息娱乐系统及基于视觉的安全系统。

2013-02-27 16:26

同步时钟是指发送时钟和接收时钟是由同一个MMCM或PLL生成,两者之间有明确的相位关系。

2020-09-23 11:25

强大的时钟管理块(CMT),结合了锁相环(PLL)和混合模式时钟管理器(MMCM) 模块,可实现高精度和低抖动;

2023-10-30 16:02