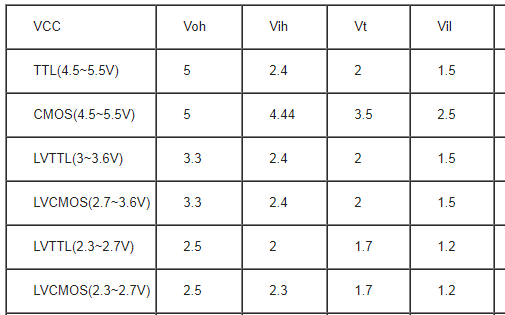

电路设计中,经常遇到各种不相同的逻辑电平。常见的逻辑电平如下: TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的 LVDS

2022-10-27 10:39

深入解析SN65EPT23:3.3V ECL差分LVPECL/LVDS到LVTTL/LVCMOS转换器 在电子设计领域,信号电平转换是一个常见且关键的需求。今天我们来详细探讨德州仪器(TI

2025-12-24 17:45

现代混合信号PCB设计的另一个难点是不同数字逻辑的器件越来越多,比如GTL、LVTTL、LVCMOS及LVDS逻辑,每种逻辑电路的逻辑门限和电压摆幅都不同,但是,这些不同逻辑门限和电压摆幅的电路必须共同设计在一块PCB上。

2019-12-10 15:28

现代混合信号PCB设计的另一个难点是不同数字逻辑的器件越来越多,比如GTL、LVTTL、LVCMOS及LVDS逻辑,每种逻辑电路的逻辑门限和电压摆幅都不同,但是,这些不同逻辑门限和电压摆幅的电路必须

2019-09-27 14:46

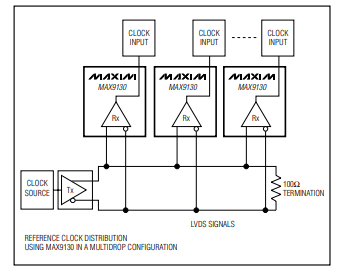

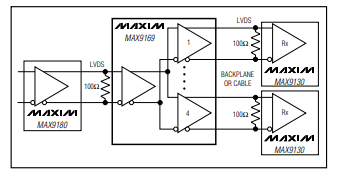

LVDS差分输入,并将其转换为LVTTL/LVCMOS输出。当输入无驱动和开路、断路或短路时,安全失效特性将设置高输出。器件支持宽共模电压输入范围,从而允许驱动器和接收器之间存在地电位差和共模噪声。MAX9130符合ANSI/TIA/EIA-644 LVDS标准。

2025-05-19 10:55

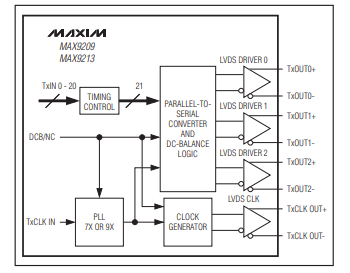

MAX9209/MAX9213将21位的LVTTL/LVCMOS并行输入数据串行化为三路LVDS输出。第四路LVDS输出为并行速率时钟,为解串器提供时钟。 MAX9209/MAX9213具有

2025-05-28 18:14

特殊功能的互连、逻辑互连中的电流倒灌问题、以及逻辑电平的转换等。 1、常见逻辑电平 常见的逻辑电平如下: 单端:TTL、CMOS、LVTTL、LVCMOS、GTL、BTL、ETL、GTLP

2021-01-02 09:45

MAX9169/MAX9170是低抖动、低电压、差分LVDS/LVTTL至LVDS中继器,尤其适合于那些要求高速数据或时钟分配、且尽可能减小功耗和尺寸以及噪声的应用。器件接收单路LVDS

2025-05-19 09:30

SN65LVELT22:3.3V 双路 LVTTL 至差分 LVPECL 转换器评测 在电子设计领域,信号转换与传输是一个关键环节。今天,我们要深入探讨德州仪器(TI)的一款产品

2025-12-25 11:10

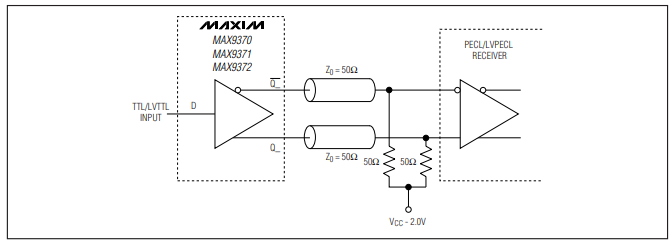

MAX9370/MAX9371/MAX9372是LVTTL/TTL到差分LVPECL/PECL电平转换器,设计应用于高速通信信号和时钟驱动器。MAX9370/MAX9372是双路LVTTL/TTL到

2025-05-19 10:22