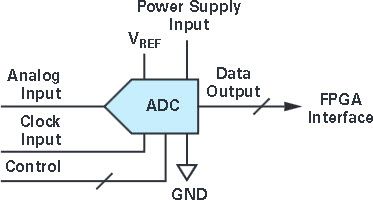

本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及

2025-07-29 10:01

。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23

使用的AD芯片是ADI的AD9653,125M16bit高精度高速ADC,用到的采样速率是80M。其SPI配置会单独开一篇来讲,SPI配置里面有个大坑,本来以为调好了的,后来又发现了问题,调了三天才定位到问题在哪,这就是硬件的魅力(坑爹)所在了吧。这里主要介绍FPGA

2023-04-03 10:28

本文讨论了标准接口 — SPI、I2C、SPORT、LVDS 和 JESD204A——用于将 FPGA 连接到 ADC。随着数据速率的进一步提高,FPGA与

2022-12-21 10:57

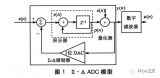

1.205 kHz 的输入进行数字化的模数转换器 (ADC)。若让 FPGA 的 LVDS 输入(而不是外部比较器)结合增量调制器 ADC 架构,仅需一个电阻器和一个

2017-11-17 01:34

LVDS是一种低压低功耗的高速串行差分数据传输标准,在高速数据互联和数据通信领域得到广泛的应用,主流的FPGA器件都集成了高速的LVDS收发器。

2024-04-26 09:50

超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据接收为例,从信号传输和数据解码两方面,详述了实现

2017-11-17 10:40

什么是LVDS,LVDS的全称是Low-Voltage Differential Signaling ,即低电压差分信号。LVDS可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。

2020-11-01 10:03

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些

2018-04-26 11:53

摘要:总线型低压差分信号(BLVDS)是一种性能优良的物理层接口标准。本文介绍一种基于总线型LVDS的通信系统方案,以及利用FPGA芯片实现系统核心模块的设计方

2009-06-20 13:48