。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23

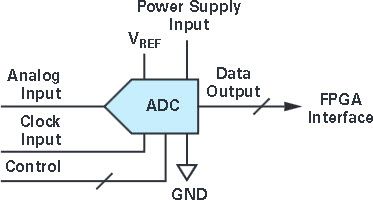

本文讨论了标准接口 — SPI、I2C、SPORT、LVDS 和 JESD204A——用于将 FPGA 连接到 ADC。随着数据速率的进一步提高,FPGA与

2022-12-21 10:57

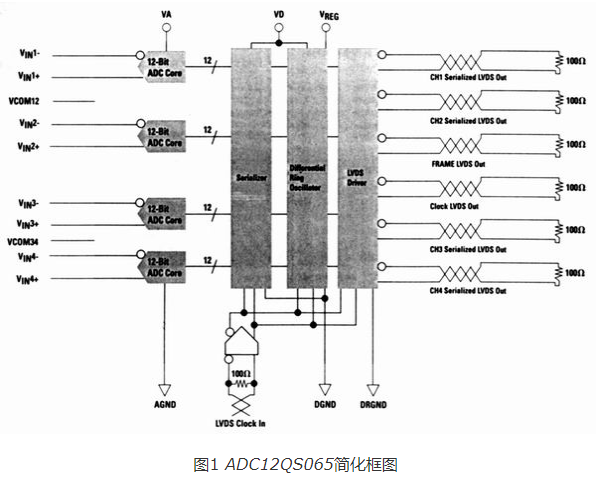

超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据接收为例,从信号传输和数据解码两方面,详述了实现

2017-11-17 10:40

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些

2018-04-26 11:53

什么是LVDS,LVDS的全称是Low-Voltage Differential Signaling ,即低电压差分信号。LVDS可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。

2020-11-01 10:03

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2020-10-10 09:25

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2023-02-09 09:48

在输入信号转换数字数据之后,必须传输它们到DSP或ASIC/FPGA进行处理。流行的全差分输出信号传输是方便的。全差分的输出信号通过两条对称线给出和吸收电流。这种信号传输的一个例子是LVDS(低压差分信号)格式。ADC

2020-04-04 17:43

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本

2022-04-21 08:55

本作品是基于FPGA的ADC0809采集控制电路。ADC0809是美国国家半导体公司生产的CMOS工艺8通道,8位逐次逼近式A/D模数转换器。其内部有一个8通道多路开关,它可以根据地址码锁存译码后的信号,只选通8

2017-11-28 17:48