转自FPGA开发圈2016-10-19I/O接口标准1.单端信号接口标准 LVTTL和LVCMOS(JESD8-5,JESD8-B) SSTL(JESD8-8,JESD8-9B,JESD8-15

2021-11-10 12:50

) LVTTL和LVCMOS结构通常是简单的push-pull。最简单的例子就是CMOS反向器,需要满足的唯一参数是VIL/VIH,VOL/VOH以及驱动电流,接口标准相对易于实现。其输入和输出参数见下面的表格

2017-11-10 14:49

大家好现在我在spartan6上做一个实验。当输入的iostandard是lvcmos25或lvcmos33时,生成的位文件都是一样的。当输入的iostandard是lvcmos18时,生成的位文件

2019-07-25 12:33

亲爱的先生,7系列HR bank支持某些I / O标准的未校准输入终端,可以减少对外部电阻的需求。I / O Standrds LVCMOS18和LVCMOS33是否支持未校准的输入端接?

2020-08-24 09:28

大家好,我需要连接DA转换器(AD9744)和Virtex 6 FPGA。我正在考虑直接使用LVCMOS25接口而不是使用电平转换器来处理来自FPGA的信息位到DAC(更少的空间)。 DA的特点是

2020-06-03 14:16

大家好, LVCMOS33和LVCMOS25可以位于Spartan-6系列FPGA的同一个存储区吗?对于Virtex-6和7系列FPGA,同样的问题是什么?谢谢。最好的祝福。以上来自于谷歌翻译以下

2019-05-29 10:34

是否可以将Spartan3 FPGA的3.3V LVCMOS o / ps连接到Virtex 5的2.5V LVCMOS输入,反之亦然。

2020-06-16 14:42

嗨,在ug810_KC705_Eval_Bd.pdf(v1.6.1)中,在第53页 - 表1-27:与FPGA U1的GPIO连接,GPIO_SW_C的IOSTANDARD是LVCMOS15。但是在

2019-09-25 07:43

手册上说CDCLVD2102前端输入可以为2.5V LVCMOS电平,可我前端时钟输入为3.3V LVCMOS电平,手册上要求进行输入摆幅控制,并且要求3.3 V LVCMOS clock

2025-01-22 07:39

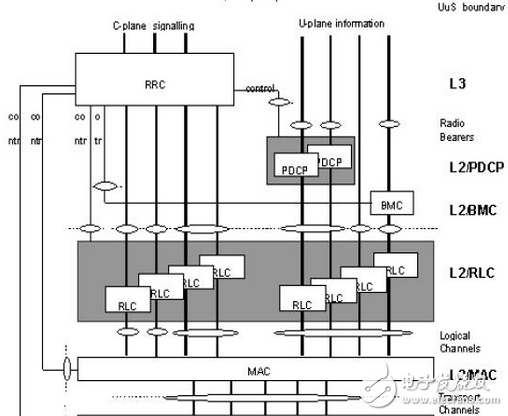

Uu接口协议栈结构 Uu协议结构Uu

2009-11-28 17:14