大家好现在我在spartan6上做一个实验。当输入的iostandard是lvcmos25或lvcmos33时,生成的位文件都是一样的。当输入的iostandard是lvcmos18时,生成的位文件

2019-07-25 12:33

亲爱的先生,7系列HR bank支持某些I / O标准的未校准输入终端,可以减少对外部电阻的需求。I / O Standrds LVCMOS18和LVCMOS33是否支持未校准的输入端接?

2020-08-24 09:28

input swing needs to be limited to VIH≤VCC。请问我可以通过分压的方式实现吗,输入时钟信号为60MHz。这样分压处理会不会引起时钟波形失真或者抖动?如果不可以,怎么将3.3V LVCMOS转换成2.5V

2025-01-22 07:39

电子发烧友网为你提供详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮

2021-04-09 08:45

Hi, 请问为什么把一个5ppm 50MHz TCXO产生的clipped-sine wave 时钟源信号送入一个输出信号模式为LVCMOS的时钟buffer 后再把buffer输出的

2018-08-22 09:35

大家好, LVCMOS33和LVCMOS25可以位于Spartan-6系列FPGA的同一个存储区吗?对于Virtex-6和7系列FPGA,同样的问题是什么?谢谢。最好的祝福。以上来自于谷歌翻译以下

2019-05-29 10:34

是否可以将Spartan3 FPGA的3.3V LVCMOS o / ps连接到Virtex 5的2.5V LVCMOS输入,反之亦然。

2020-06-16 14:42

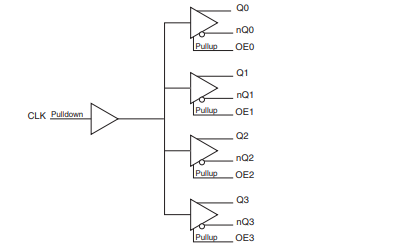

854105是一种低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS时钟扇出缓冲区。利用低压差分信号(LVDS),854105提供了一种低功耗、低噪声的解决方案,用于将时钟信号分布在100Ω的受控阻抗上。8

2019-07-22 08:00

嗨,在ug810_KC705_Eval_Bd.pdf(v1.6.1)中,在第53页 - 表1-27:与FPGA U1的GPIO连接,GPIO_SW_C的IOSTANDARD是LVCMOS15。但是在

2019-09-25 07:43

转自FPGA开发圈2016-10-19I/O接口标准1.单端信号接口标准 LVTTL和LVCMOS(JESD8-5,JESD8-B) SSTL(JESD8-8,JESD8-9B,JESD8-15

2021-11-10 12:50