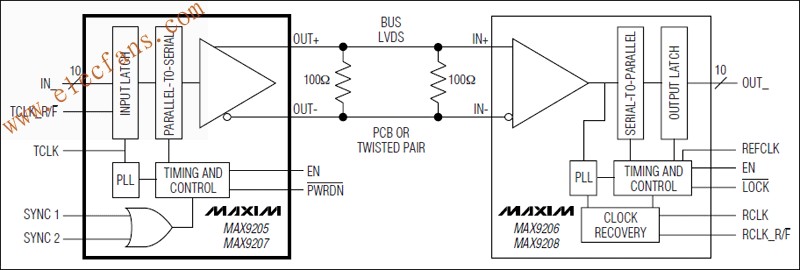

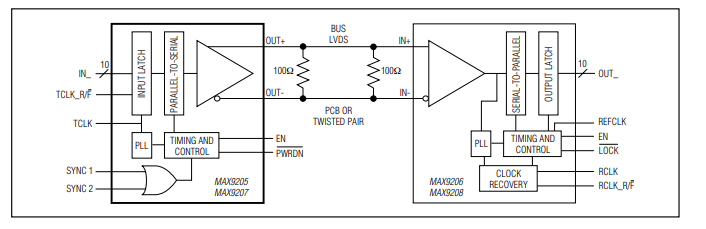

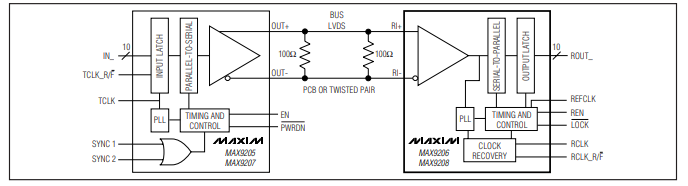

MAX9205/MAX9207串行器将10位宽度并行LVCMOS/LVTTL数据转换为串行高速总线LVDS数据流。串行器与解串器配对使用,如MAX92

2010-12-21 09:57

MAX9234/MAX9236/MAX9238可将三路LVDS串行输入解串为21路单端LVCMOS/LVTTL输出。随LVDS数据流接收到的并行LVDS时钟提供解串定时。输出具有独立的供电引脚,允许1.8V至5V的输出逻辑电平。

2012-11-08 10:54

数据输入转换成21路单端LVCMOS/ LVTTL输出.单端数据和时钟输出可编程±2%, ±4%或没有扩展频谱,以降低EM

2010-02-14 10:18

OmniClock系列支持从8 kHz到200 MHz的任意输出频率,有三个单端时钟输出(LVCMOS/LVTTL),两者可以组合成一个差分输出(LVPECL、LVDS、HCSL / CML),令设计人员可替代多个晶体和/或振荡器,降低整体系统成本。

2016-07-07 13:49

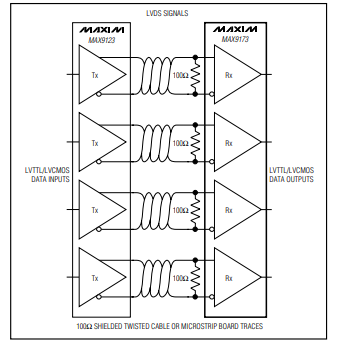

MAX9205/MAX9207串行器将10位宽度并行LVCMOS/LVTTL数据转换为串行高速总线LVDS数据流。串行器与解串器配对使用,如MAX9206/MAX9208解串器,完成将串行输出再转换为10位宽度的并行数据。

2025-05-29 09:23

MAX9242, MAX9244, MAX9246, MAX9254 21位解串器,提供可编程频谱扩展和直流平衡 MAX9242/MAX9244/MAX9246/MAX9254能够将三路LVDS串行数据解串为21位单端LVCMOS/LVTTL输出

2009-08-20 10:01

I/O接口标准 1.单端信号接口标准 LVTTL和LVCMOS(JESD8-5,JESD8-B) SSTL(JESD8-8,JESD8-9B,JESD8-15) HSTL(JESD8-6

2017-11-10 14:49

MAX9206/MAX9208解串器将高速串行BLVDS数据流转换位10位宽度的并行LVCMOS/LVTTL数据和时钟。解串器与串行器配对使用,如MAX9205/MAX9207串行器,完成将10位

2025-05-29 09:17

电路设计中,经常遇到各种不相同的逻辑电平。常见的逻辑电平如下: TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的 LVDS

2022-10-27 10:39

(250MHz)。传输介质可以是印刷电路(PC)板覆铜线或电缆。 MAX9173接收四路LVDS差分输入,转换为对应的LVCMOS/LVTTL输出。MAX9173具有高阻输入,当用于点对点连接时,需要外接终端电阻。

2025-05-19 09:35