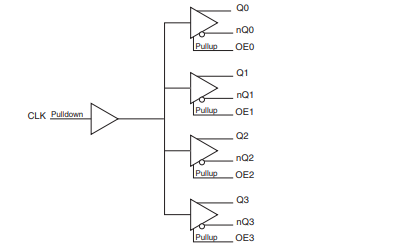

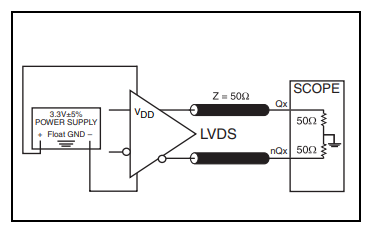

854105是一种低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS时钟扇出缓冲区。利用低压差分信号(LVDS),854105提供了一种低功耗、低噪声的解决方案,用于将时钟信号分布在100Ω的受控阻抗上。854105接受

2019-07-22 08:00

电子发烧友网为你提供详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮

2021-04-09 08:45

, and at-speed BIST.Each serializer block transforms an 18-bit parallel LVCMOS/LVTTL data bus into a single Bus LVDS data stream wit

2009-10-13 10:03

The MAX9205/MAX9207 serializers transform 10-bitwideparallel LVCMOS/LVTTL data into a serial

2012-12-17 10:34

The DS90C383 transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage

2009-10-14 10:22

The DS90CR287 transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage

2009-10-14 09:24

The DS90CR485 serializes the 24 LVCMOS/LVTTL doubleedge inputs (48 bits data latched in per clock

2009-10-14 09:45

The DS90CR285 transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage

2009-10-14 09:39

ICS854105I是一个低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS时钟扇出缓冲区。利用低压差分信号(LVDS),ICS854105I提供了一种低功耗、低噪声的解决方案,用于在

2019-07-22 08:00

信号的逻辑电平经历了从单端信号到差分信号、从低速信号到高速信号的发展过程。最基本的单端信号逻辑电平为CMOS、TTL,在此基础上随着电压摆幅的降低,出现LVCMOS、LVTTL等逻辑电平,随着信号速率的提升又出现ECL、PECL、LVPECL、LVDS、CML等差

2021-01-05 17:32