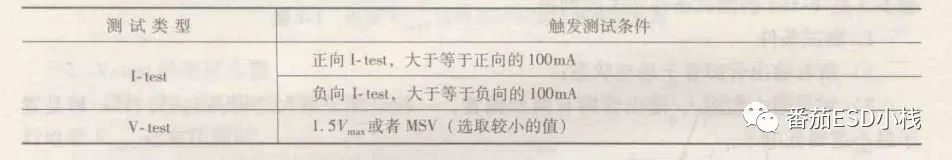

目前通用的Latch-up测试标准是JESD78E。该标准中将Latch-up测试分为两种:1.电流测试 I-test,用于测试非电源管脚;2.电压测试 V-test 用于测试电源管脚。

2023-06-12 16:27

ESD,EOS,Latch-up都是芯片在制造,运输,使用过程中的风险源,他们会对芯片造成不同程度的物理损伤。

2023-06-12 16:25

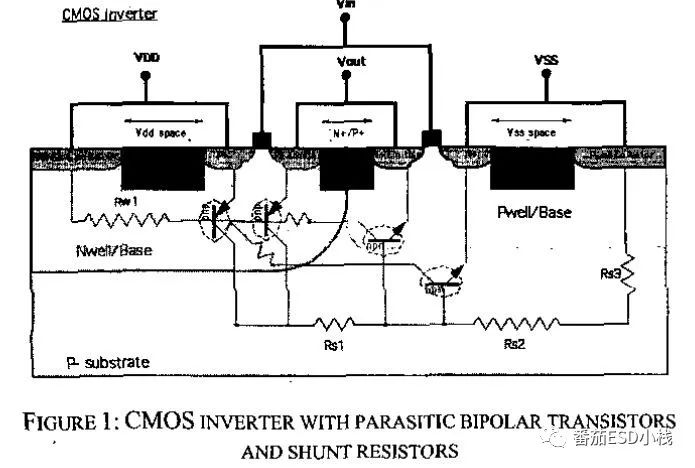

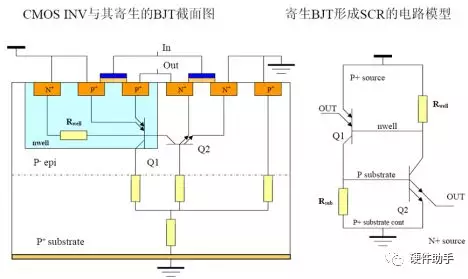

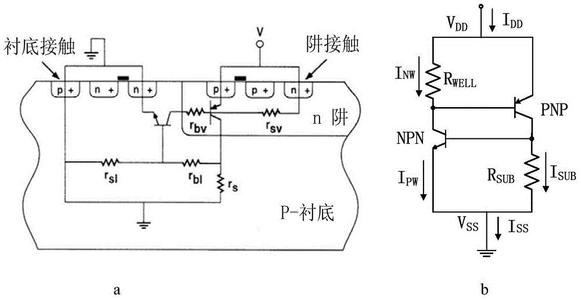

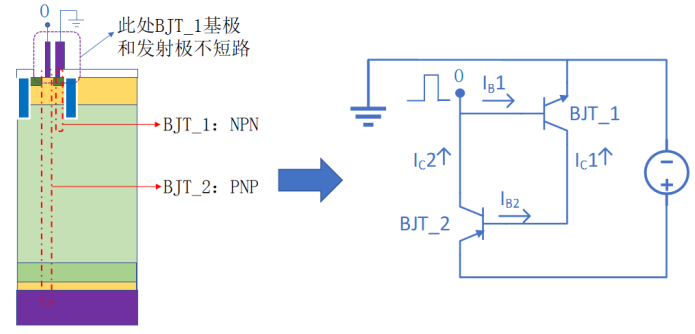

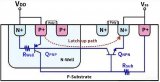

本篇主要针对CMOS电平,详细介绍一下CMOS的闩锁效应。 1、Latch up 闩锁效应是指CMOS电路中固有的寄生可控硅结构(双极晶体管)被触发导通,在电源和地之间存在一个低阻抗大电流通路,导致

2020-12-23 16:06

闩锁效应,latch up,是个非常重要的问题。现在的芯片设计都不可避免的要考虑它。我今天就简单地梳理一下LUP的一些问题。

2023-12-01 17:11

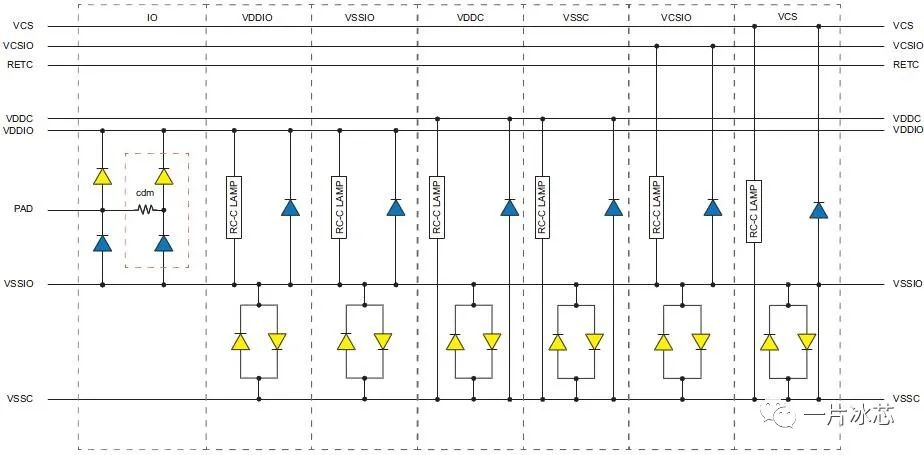

一般多电源轨的ESD方案如图1所示。最左侧两个diode用于HBM(Human Body Model)保护

2023-10-31 17:16

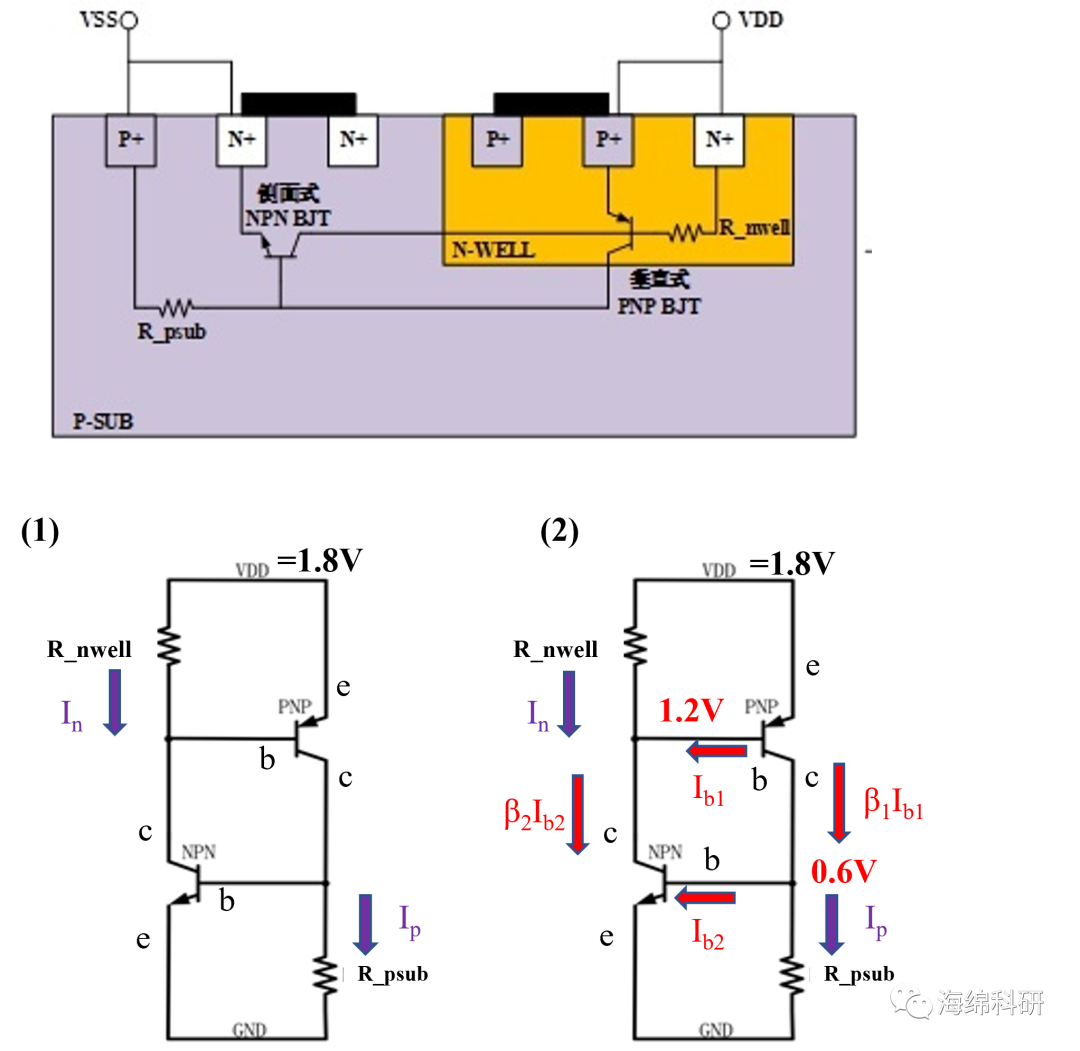

闩锁效应:实际上是由于CMOS电路中基极和集电极相互连接的两个BJT管子(下图中,侧面式NPN和垂直式PNP)的回路放大作用形成的

2023-12-01 14:10

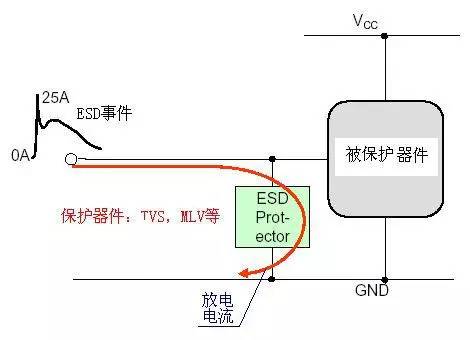

雷卯电子提供满足基础静电、浪涌保护的器件同时,研发出更高功能的大电流、防死锁的高功率ESD器件,即防Latch-up。 Latch up 是指cmos晶片中, 在电源power VDD和地线GND

2020-03-15 10:49

在前文的PNP结构中,我们描述了一种现象,如果IGBT中的两个BJT都处于工作状态,那么就会发生失控,产生latch-up现象。

2023-11-29 12:43

clamps, TransZorb™, and zener diodes are considered. Internal latch-up is explained. Protection of vulnerable CMOS devic

2009-04-24 16:37

在CMOS电路中,存在寄生的PNP和NPN晶体管,它们相互影响在VDD与GND间产生一低阻通路,形成大电流,烧坏芯片,这就是闩锁效应,简称latch-up。

2025-07-03 16:20