ncp1234的latch脚怎么用 ncp1234的latch脚是一种用于控制数据输入和输出的引脚,在数字电路设计中起着重要的作用。 ncp1234的latch脚的功

2023-12-07 16:52

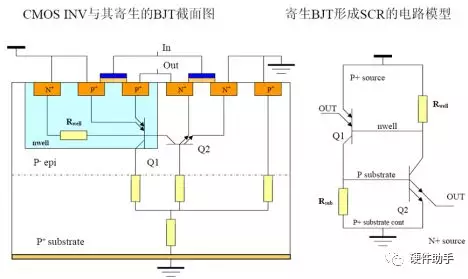

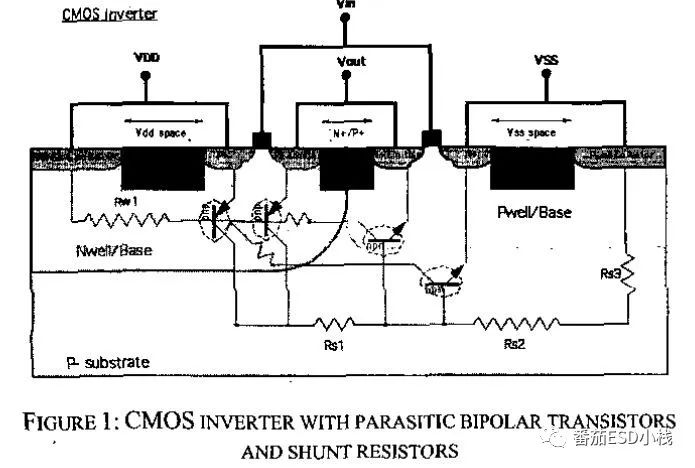

本篇主要针对CMOS电平,详细介绍一下CMOS的闩锁效应。 1、Latch up 闩锁效应是指CMOS电路中固有的寄生可控硅结构(双极晶体管)被触发导通,在电源和地之间存在一个低阻抗大电流通路,导致电路

2020-12-23 16:06

有朋友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

2024-02-20 16:12

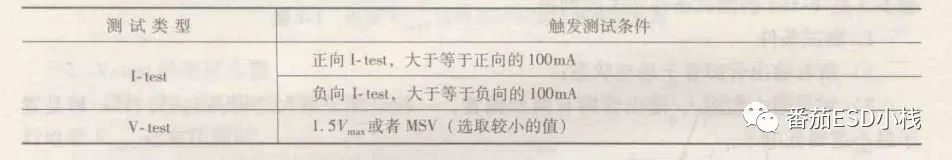

目前通用的Latch-up测试标准是JESD78E。该标准中将Latch-up测试分为两种:1.电流测试 I-test,用于测试非电源管脚;2.电压测试 V-test 用于测试电源管脚。

2023-06-12 16:27

当 E = 1 时,latch直传(transparent),D端信号的变化会即时反应在Q端;

2023-06-27 14:55

ESD,EOS,Latch-up都是芯片在制造,运输,使用过程中的风险源,他们会对芯片造成不同程度的物理损伤。

2023-06-12 16:25

锁存器(Latch),是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2023-06-02 11:32

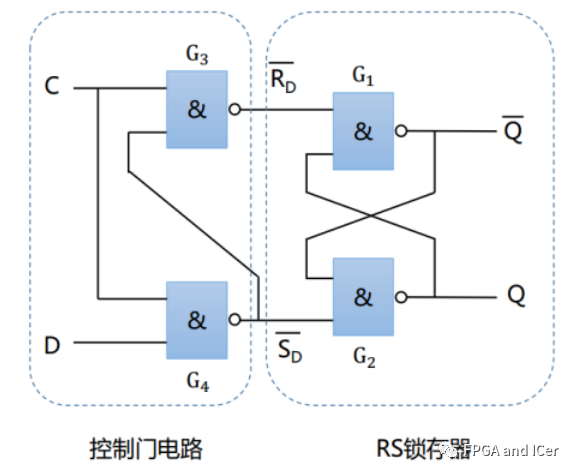

本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10

锁存器( latch)是电平触发的存储单元,数据存储的状态取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2023-06-02 15:45

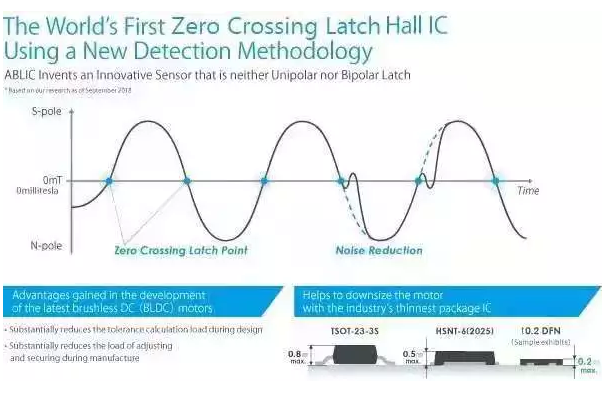

ABLIC 艾普凌科于今天下午2:00,在2019年慕尼黑 (上海) 电子展(展位号:E4馆4525号)介绍展示全球首款 “Zero Crossing Latch 霍尔 IC”,诚邀您来参加。

2019-03-20 13:04