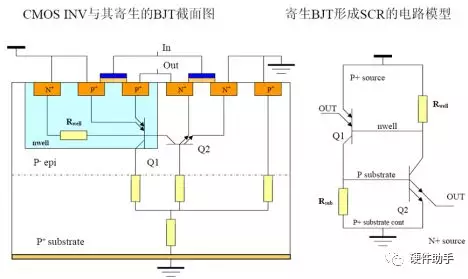

本篇主要针对CMOS电平,详细介绍一下CMOS的闩锁效应。 1、Latch up 闩锁效应是指CMOS电路中固有的寄生可控硅结构(双极晶体管)被触发导通,在电源和地之间存在一个低阻抗大电流通路,导致电路

2020-12-23 16:06

有朋友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

2024-02-20 16:12

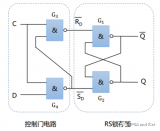

本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10

D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26

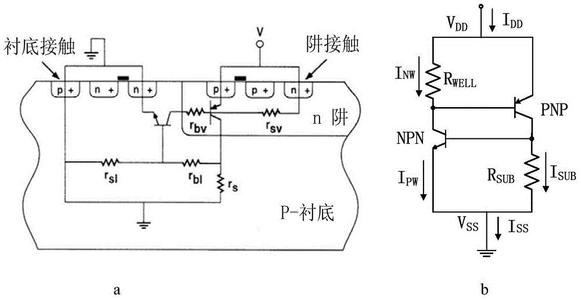

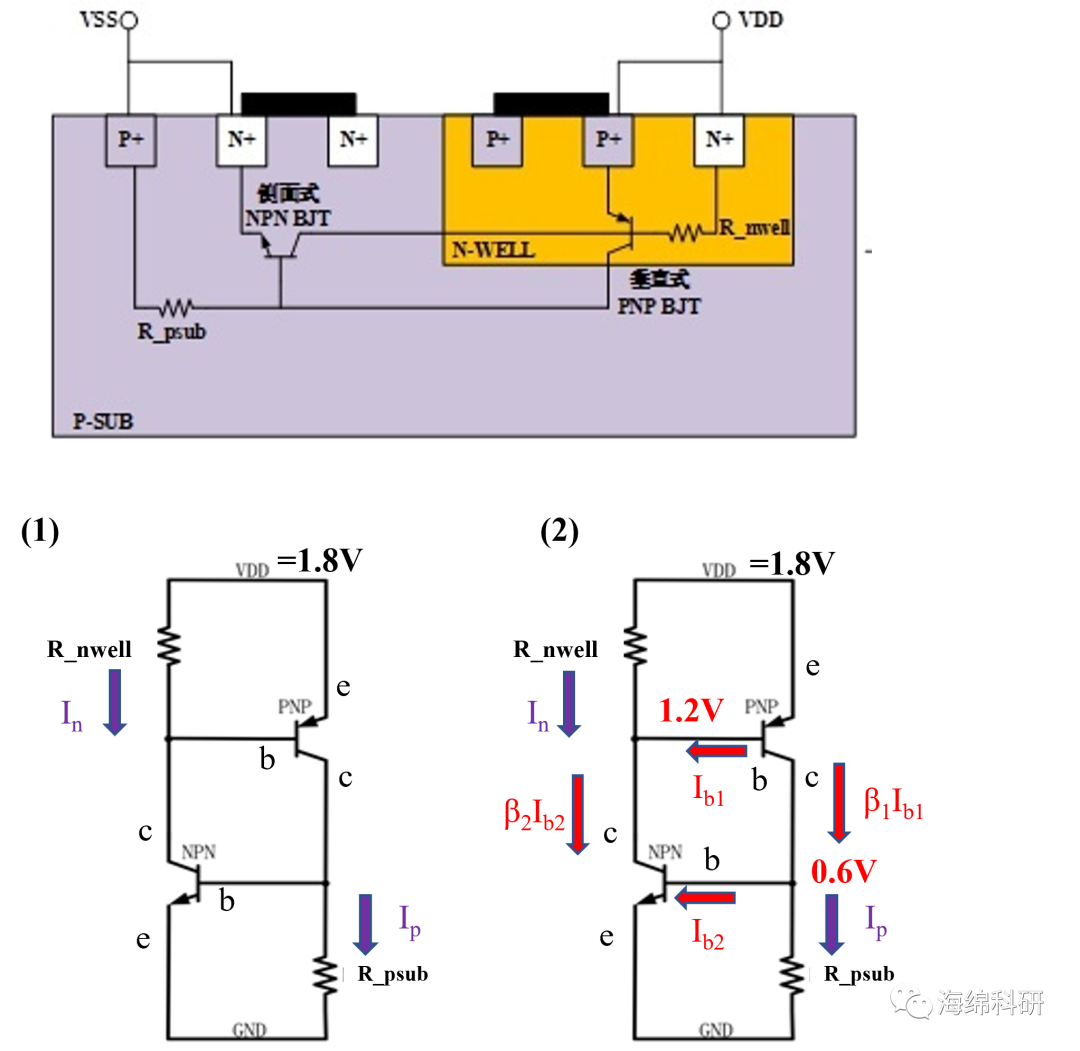

闩锁效应,latch up,是个非常重要的问题。现在的芯片设计都不可避免的要考虑它。我今天就简单地梳理一下LUP的一些问题。

2023-12-01 17:11

闩锁效应:实际上是由于CMOS电路中基极和集电极相互连接的两个BJT管子(下图中,侧面式NPN和垂直式PNP)的回路放大作用形成的

2023-12-01 14:10

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,避免使用Latch(锁存器)一直是个绕不开的话题,本文结合网上的文章,并根据示例介绍如何在实际设计中避免Latch。

2023-08-08 09:55

latch是电平触发,register是边沿触发,register在同一时钟边沿触发下动作,符合同步电路的设计思想,而latch则属于异步电路设计,往往会导致时序分析困

2017-02-11 12:39

锁存器是一种在异步时序电路系统中,对输入信号电平敏感的单元,用来存储信息。一个锁存器可以存储1bit的信息,通常,锁存器会多个一起出现,如4位锁存器,8位锁存器。

2020-10-05 14:28

、降压型变换器均衡充电、电感均衡充电等。 锂电池保护板均衡原理 锂电池在充电过程中,每节锂电池都设有一个均衡电路,在充电时通过锂电池保护板的均衡电路来控制每节电池的电压,使每一串电池保持相同状态,保证锂电池的性。

2019-07-12 09:26