一种新的转换器接口的使用率正在稳步上升,并且有望成为未来转换器的协议标准。这种新接口——JESD204——诞生于几年前,其作为转换器接口经过几次版本更新后越来越受瞩目,效率也更高。随着转换器分辨率

2019-06-17 05:00

JESD204是什么?JESD204标准解析,为什么我们要重视它?

2021-04-13 06:14

到串行接口(JESD204)的转变。JESD204由JEDEC开发(http://www.jedec.org/,全称是联合电子设备工程委员会,历史背景请参考http://www.jedec.org

2019-05-29 05:00

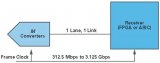

2006年4月,JESD204最初版本发布。该版本描述了转换器和接收器(通常是FPGA或ASIC)之间数Gb的串行数据链路。在 JESD204的最初版本中,串行数据链路被定义为一个或多个转换器和接收器之间的单串行通道。

2021-01-04 16:27

嗨,我正在使用ISE14.6和Vivado 2013.2并且我曾要求获得JESD204的评估许可证,当我将许可证映射到VIvado时,我也得到了相同的结果,JESD204 LogicIP核心未突出

2020-03-11 06:05

本次研讨会视频将从原始版本到现在的“B”版本简要介绍JESD204标准。此外,还将介绍与JESD204等高速串行接口相关的常见“高性能指标”。研讨会中涉及的话题也适用于使用类似高速串行接口的应用。

2019-07-05 06:19

目前,我在设计中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D转换器AD9683转换完成后的数据。但是JESD204 IP核的端口很多,我不知道应该如何将AD9683

2023-12-15 07:14

。目前,我在设计中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D转换器AD9683转换完成后的数据。但是JESD204 IP核的端口很多,我不知道应该如何将AD9683

2018-09-05 11:45

追溯到dcp,结果发现tx_core_clk和rx_core_clk被限制在6.4ns(156.25MHz),就像原来的JESD204内核一样。在我的设计中,这些时钟是250MHz,并且在顶级xdc文件

2018-10-19 14:37

为什么JESD204内核不使用GTX通道绑定功能来对齐通道?我试图从AD接收数据,AD使用JESD204B协议传输数据。我的计划是使用GTX核心并自己编写JESD部分。我的项目需要两个车道,我在初始

2020-08-18 10:03