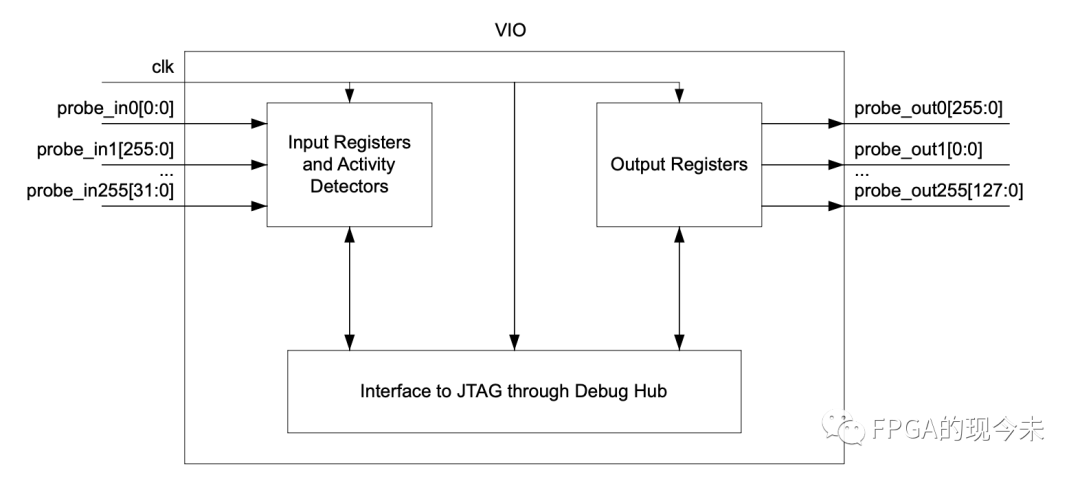

一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

2022-06-12 15:51

debug,尤其是通信芯片的debug,可以有很多的方法。一个数据帧从进入到输出,可以在通路上的关键节点处设置监测如各种计数器等,可通过VIO(xilinx)定时上报实时状态。可以把VIO的各个

2019-07-19 10:19

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的。其实Xilinx还提供了一个叫VIO的core,可以动态改变FPGA内部某个信号的值,但是一直没有用过,一来对于以前的项目来说,没有应用场景,通过寄存器就可以配置了;二来感觉这个东西不是很“实用”。

2023-12-11 18:26

Xilinx ISE使用错误和警告汇总,具体的跟随小编一起来了解一下。

2018-07-13 06:10

本文提出了一种新方法,通过使用点到平面匹配将VIO/VSLAM系统生成的稀疏3D点云与数字孪生体进行对齐,从而实现精确且全球一致的定位,无需视觉数据关联。所提方法为VIO/VSLAM系统提供了紧密

2024-12-13 11:18

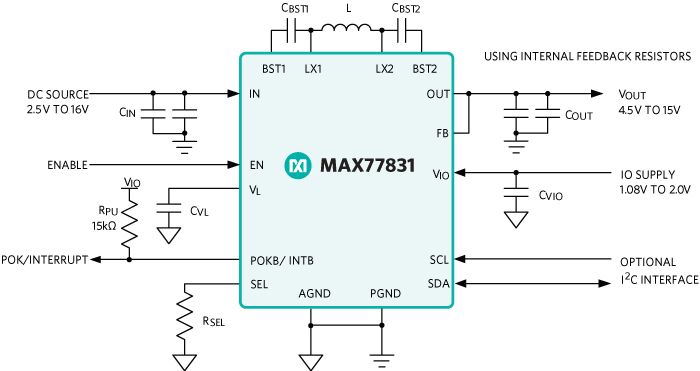

MAX77831为高效率、降压-升压稳压器,具有宽输入和输出范围,具有许多有用的特性。除了主输入电压外,它还需要一个 1.08V 至 2V 的电源来提供 VIO引脚,该电压设置数字引脚(EN、POKB/INTB、SCL 和 SDA)的逻辑电平。

2023-02-02 16:52

赛灵思 ISE 12设计套件利用智能时钟门控技术将动态功耗降低30% 1)赛灵思今天要宣布什么消息? ISE® 12设计套件不仅实现了功耗与成本的突破性优化,而且为逻辑、嵌入式、DSP和系统设计人

2018-07-02 06:20

用了半个多月的ISE,几乎全是自学起来的,碰到了很多很多让人DT好久的小问题,百度也百不到,后来还是都解决了,为了尽量方便以后的刚学ISE的童鞋不再因为一些小问题而纠结,把这几天的经验总结了一下。

2017-02-11 06:53

版本迁移的操作想必大家已经做过不少了,其中包括从ISE转换到vivado与vivado老版本迁移到新版本。郑智海同学给大家介绍了一下如何把工程从ISE迁移到vivado中。

2023-01-30 09:11

在使用ISE进行FPGA的bit文件下载时,经常会遇到下载失败的问题,提示:"DONE did not go high".

2017-02-11 14:20